Dobrý článek

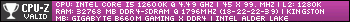

Conroe nebo Allendale

http://www.zive.cz/h/Uzivatel/AR.asp?ARI=132802

CPUID 6F1 - revize A1

První funkční model dokončený 10. října 2005. Obsahuje dvě jádra a sdílenou 4 MB L2 cache. Jedná se o vývojový prototyp, který není určen k prodeji.

Způsob, kterým se dá zjistit datum dokončení čipu, si z pochopitelných důvodů ponechám pro sebe jako moje know-how.

CPUID 6F2 - revize L2

Přestože stepping u tohoto modelu dává najevo, že se jedná o jakýsi historický kousek, není tomu tak. Toto je totiž poměrně nový (13. července 2006) zástupce řady a od ostatních se liší tím, že obsahuje jen 2 MB L2 cache. Jedná se o kus, který se až nyní začíná objevovat v obchodech a to konkrétně v procesoru Core 2 Duo E4300. Postupně se objeví i v modelech E6300, E6400, mobilních Core 2 Duo řady T5x00 a u některých níže taktovaných Xeonů řady 51x0.

CPUID 6F4 - revize B0

Druhý dokončený model, který se objevoval na jaře 2006 (finalizován byl 12. března 2006). Jedná se taktéž o vývojový prototyp, který není určen k prodeji. Má dvě jádra a 4 MB cache.

CPUID 6F5 - revize B1

Revize ze dne 1. května 2006, kterou Intel posílal do testů. Jedná se stále o prototyp (ano, Intel posílal do časopisů k testům prototyp!). Stejně jako B0 obsahuje dvě jádra a 4 MB cache. Jedná se o první kusy, u kterých Intel začal kalibrovat digitální teplotní čidlo a které patrně byly původně plánovány k prodeji.

Je možné, že některé kusy 6F5 byly dodány do prodeje, ale to patrně jen OEM zákazníkům, nikoli v BOX balení do maloobchodu. Veřejně přístupná dokumentace Intelu totiž obsahuje k tomuto jádru seznam chyb (Specification Update). Uvedená skutečnost je podivná z toho důvodu, že běžně se jakékoli údaje o prototypech nezveřejňují.

CPUID 6F6 - revize B2

V zásadě jen mírně upravená revize B1, u které byly zjištěny určité blíže nespecifikované potíže, a proto musela být urychleně „záplatována“ revizí B2. Datum dokončení je 23. května 2006, tedy jen tři týdny po B1. Toto jádro posloužilo k uvedení Xeonů řady 5100 a mobilních i desktopových Core 2 Duo a doposud na něm byly založeny všechny uvedené procesory vyjma čtyřjádrových. Podle Intelu je počet v něm přítomných chyb zcela identický s B1, což je ale poměrně nepravděpodobné (připravit revizi stojí hodně peněz, takže v tom nějaký ten důvod, který si výrobce nepřeje zveřejnit, jistě bude).

Momentálně Intel začíná dodávat nové série (sSpec) procesorů Core 2 Duo s revizí B2, které mají významně sníženou spotřebu při nevytížení - z limitu TDP 22W se dostávají na 12W. V tomto případě se ale nejedná o úpravu jádra, ale patrně o přeprogramování jeho úsporných režimů.

CPUID 6F7 - revize B3

Toto jádro je dnes používáno jen u čtyřjádrových procesorů Kentsfield (Core 2 Quad) a Clovertown (Xeon řady 5300). Vzniklo 12. července 2006, tedy v době, kdy se původní 6F6 již vyrábělo pro prodej. Proč ho Intel uvedl, mi není známé. Ani počet chyb to nevysvětluje, je jich totiž téměř stejný počet jako u 6F6. V zásadě se proto nabízí dvě teorie:

buďto 6F6 nebylo pro čtyřjádrové procesory vhodné (čtyřjádrový je slepenec dvou dvoujádrových, tedy se jedná o dva klienty FSB a to zatěžuje sběrnici),

nebo se prostě jednalo o standardní vývojové jádro, které ale nakonec nebylo v důsledku urychlení vývoje dokončeno včas, tj. před uvedením (to bylo původně plánovalo zhruba na konec září).

Intel v současnosti neplánuje, že by se B3 objevilo i v ostatních procesorech.

CPUID 6F9 - revize ?

Nejnovější revize z 3. září 2006, opět s 4MB L2 cache. Toto jádro dosud nebylo uvedeno. Toho se dočká až patrně spolu s novým Centrinem. Tento čip má totiž obsahovat dvě zajímavé technologie:

Intel Dynamic Acceleration - Technologie, která u dvoujádrových procesorů v případě nevytížení obou jader u jednoho z nich zvýší frekvenci, a tím urychlí zpracování jednovláknových aplikací (... které nemohou z dvoujádrových procesorů benefitovat). Pokud se zatíží obě jádra, frekvence se opět vrátí k normálu, jinak by došlo k překročení termálních specifikací (TDP).

Dynamická změna FSB - Jak už název napovídá, půjde o to, že v případě nevytížení budou procesor a čipset schopni snížit frekvenci FSB, čímž dojde k úspoře energie.

. Coz by i vysvetlovalo horsi taktovatelnost E4300.