Stránka 86 z 99

Re: INTEL News

Napsal: čtv 4. dub 2024, 10:35

od mr.qeg

Pat zřejmě mluví o Intel Foundry Services. Ty budou zřejmě dotavat z ostatních odvětví. Ono je to i logické, ty továrny musí postavit, nakoupit stroje a začít získávat zákazníky...

Re: INTEL News

Napsal: pát 26. dub 2024, 18:19

od del42sa

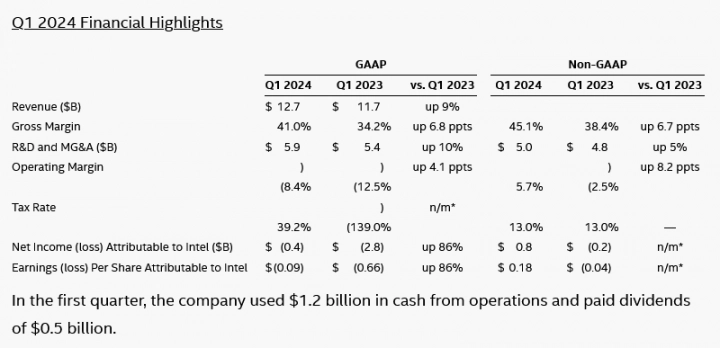

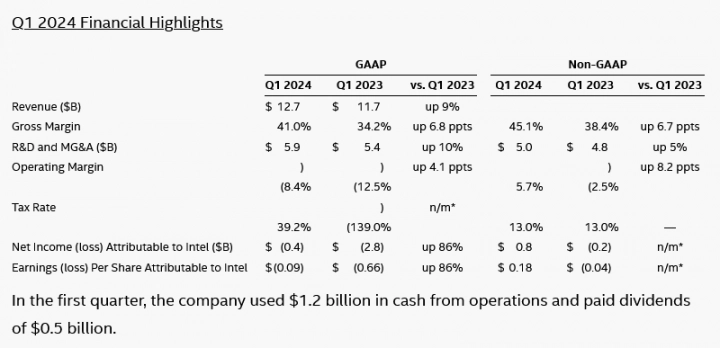

https://www.cnews.cz/clanky/intel-zase- ... cna-slaba/

opět ztráta, servery na dně, ale to nepřekvapí, nakonec Intel drží paradoxně trh PC

Re: INTEL News

Napsal: pát 26. dub 2024, 20:29

od fobos

Intel ide dole vodou... za 2 3 roky ho AMD v trzbach dobehne

Re: INTEL News

Napsal: sob 27. dub 2024, 08:44

od mr.qeg

S takovou za 2-3 roky koupí Intel Huang a to pak bude jiná jízda

Re: INTEL News

Napsal: čtv 2. kvě 2024, 15:09

od flanker

Značení Arrow Lake bdue Core Ultra 2xx, čili druhá generace Intel Core Ultra procesorů

https://videocardz.com/newz/intels-core ... ocked-skus

Re: INTEL News

Napsal: pát 31. kvě 2024, 08:47

od del42sa

https://videocardz.com/newz/intels-next ... s-leak-out

zajímavé detaily o procesorech Lunar Lake, konkrétně o architektuře "Skymont" což jsou nové e-jádra.

N3B TSCM proces

SoC N6

dekodér je nyní 9 - wide (!)

ALU je celkově 8 (!)

double digit IPC

první laptopy v říjnu

Re: INTEL News

Napsal: pát 31. kvě 2024, 09:44

od Krteq

Link na ty slidy? Z tohohle se nedá nic vyluštit

Re: INTEL News

Napsal: pát 31. kvě 2024, 09:53

od del42sa

za to já fakt nemůžu

nejspíš to bude tím, že to stále ještě není úplně veřejný údaj

https://x.com/9550pro/status/1796118604133421387

https://forums.anandtech.com/attachment ... eg.100005/

https://x.com/9550pro/status/1796118604133421387

https://forums.anandtech.com/attachment ... eg.100005/

pravděpodobně by to mohl být řešené podobně jako u

Gracemontu 2 x 3 ( ... two concurrent streams of decode that could support 3 per cycle ... ) tentokrát 3 x 3 clustery, uvidíme až se vynoří další podrobnosti.

\\ další slide ukazují:

In ST, Skymont can have 1.7x higher performance vs. Crestmont at iso-power, or 1/3rd power at iso-perf.

In MT, Skymont can have 2.9x higher performance vs. Crestmont at iso-power, or 1/3rd power at iso-perf

PS: Keller prý v Intelu pracoval dokonce na 12-wide core ...

https://x.com/much_science/status/17962 ... wsrc%5Etfw

Re: INTEL News

Napsal: pát 31. kvě 2024, 10:34

od del42sa

plus nějaká analýza těch slidů od Chipsandcheese:

Tremont massively increased structure sizes compared to Goldmont Plus. Those increases likely played a large role in its huge 30+% IPC gains. If Skymont gets similar increases, its structure sizes would be very close to Golden Cove’s.

https://chipsandcheese.com/2024/05/30/t ... nt-slides/

jaká potom bude pointa P- jader ?

Re: INTEL News

Napsal: pát 31. kvě 2024, 11:29

od jctrnacty

Obavam se, ze jedina pointa intel prezentaci je, ze slouzi velice dobre jako toaletni papir. A to uz od roku 2017.

Re: INTEL News

Napsal: sob 1. čer 2024, 11:46

od del42sa

del42sa píše: ↑pát 31. kvě 2024, 08:47

N3B TSCM proces

SoC N6

dekodér je nyní 9 - wide (!)

ALU je celkově 8 (!)

double digit IPC

první laptopy v říjnu

pardon, v tom popisu nemělo být 8 ALU, ale 8 - wide

Re: INTEL News

Napsal: sob 1. čer 2024, 14:24

od Tralalák

Vykonávanie inštrukcii mimo poradia (out-of-order execution) vo fáze allocation Gracemontu umožňoval spracovať až 5 instrukcií (μOPs) pricházajúcích z fázy dekódovania a radu μOP Queue za cyklus. Gracemont sa zlepšil o 25% oproti Tremontu nakoľko ten je v tejto fázy pipeline len 4-wide pričom len pre porovnanie P-core Golden Cove má vo fázi Allocation spracováva až 6 instrukcií za cyklus tj. 6-wide.

No a Skymont ide ešte ďalej vo fáze allocation umožňuje spracovať až 8 instrukcií (μOPs) pricházajúcích z fázy dekódovania a radu μOP Queue za cyklus tj. 8-wide čo je zlepšenie o 33,33% oproti Crestmontu, o 60% oproti Gracemontu a až o 100% voči Tremontu.

Inými slovami:

• Tremont je 4-wide, superscalar, out-of-order core

• Gracemont je 5-wide, superscalar, out-of-order core

• Crestmont je 6-wide, superscalar, out-of-order core

• Skymont je 8-wide, superscalar, out-of-order core

Re: INTEL News

Napsal: sob 1. čer 2024, 14:54

od DOC_ZENITH

Ví se už něco o podpoře AVX512 nebo přítomnost této věci bude kriplit zbytek CPU jako doteď?

Re: INTEL News

Napsal: sob 1. čer 2024, 16:34

od jctrnacty

Podpora avx512 se nekona , jelikoz by se teplota cpu pri jejich pouziti vyrovnala teplotam ve vysoke peci. Frajeri v intelu nejsou schopni zajistit bezpečnost pri jejich pouziti.

Re: INTEL News

Napsal: sob 1. čer 2024, 17:09

od Tralalák

DOC_ZENITH píše: ↑sob 1. čer 2024, 14:54

Ví se už něco o podpoře AVX512 nebo přítomnost této věci bude kriplit zbytek CPU jako doteď?

Nepredpokladám, že by sa Intel vrátil mimo Xeonov k podpore svojim AVX512 avšak predpokladám, že v rámci reorganizácie 512bitových inštrukcií budú implementované pod pláštík AVX10.

Re: INTEL News

Napsal: sob 1. čer 2024, 18:41

od DOC_ZENITH

O AVX10 vím ale AVX10 je jen takové šplouchnutí do vody ala "něco děláme" v praxi když to CPU nebude schopné zpracovávat 512-bit vektory tak to prostě nepůjde. AVX10 je něco jako určitá generace SSE, je to jen jméno co pod sebou sdružuje určité instrukce. Podstatné je že už dnes má ve spoustě situací AMD výhodu, protože jejich procesory alespoň zpracovávaj 512-bit vektory, sice na 2 průchody ale v některejch AI výpočtech to dost pomáhá, naopak Intel se zdá se zasejvá bordel. Co teda nakonec budou tlačit? subsety AVX512 co jsou na tohle good pod pláštěnkou AVX10? Přímou podporu BF16? Nebo se bude tlačit AVX-VNNI? Nebo LAM, nebo to vše půjde boken a bude se doufat že NPU akcelerátor vše zachrání? Prostě WTF co je vlastně cílem. Všude tuna insturkcí co jsou navzájem nekompatibilní, mění se to každou generaci, nikdo neví pro co má vyvíjet/optimalizovat SW. HT je na Pcorech vypnuté proč? S takle širokou pipeline by i Ecory mohly mít HT a dost z něj těžit. Víme že Aldery/Raptory byly takovej slepenec ze zoufalství ale člověk by čekal že 2 generace poté už Intel alespoň bude mít ňákej koncept čeho vlastně chtěj dosahnout.

Re: INTEL News

Napsal: sob 1. čer 2024, 19:29

od Tralalák

Začnem od konca Alder Lake bol nedokončený Raptor Lake pri paradigmálnej zmene big.LITTLE, ktorá bola logickým vyústením už dedádu nekonkurenciaschopných litografii (výrobných procesov) Intelu voči napr. TSMC a pod.

Naspäť k Arrow Lake / Lunar Lake a ďalších. V podstate Intel prechodom na nie in-house litografie v podobe 3nm TSMC (viď. aký progres zaznamenala iGPU dlaždica postavená na TSMC v Meteor Lake) v rámci rozbehnutého vlaku vyššie uvedenenej paradigmálnej zmeny sa konečne mohol sústrediť aj na malé atómové E-jadrá a ich poriadnu evolúciu a priblíženie tak k veľkých jadrám (nie, že by P-jadrá sa ďalej neprechádzali evolúciou), inými slovami pokročilý výrobný procesor tak P ako E jadrá dokázal riadne popohnať toľko k vyššie uvedenej diléme pointe P-jadier.

AVX10 bude môcť fungovat už aj s 256bit. registrami, ktorých ale bude 2× viac ako pri 256bit. registroch AVX (ymmx). 512bit. instrukcie budú replikované tiež na 256bit. zároveň prinesie ďalšie nové operacie, ktoré v AVX-512 ešte neboli.

Pre trh samozrejme platí čo implementuje v jednotlivých segmentoch ten, ktorá na trhu ma podiel podľa segmentu 70% - 85% a nie ten čo 15% - 30% takže nástup a implementácia AVX10 má omnoho širšie využitie a rozšíriteľnosť nakoľko naďalej bude umožňovat aj 512bit. verziu, která bude plne ekvivalentná s AVX-512 schopnosťami a výkonem (samozrejme až na nové fíčuri, ktoré AVX-512 už nebude mať) a zároveň táto podpora je na rozdiel od podpory 128bit. a 256bit. inštrukcií nepovinná a tudíž volitelná.

Re: INTEL News

Napsal: sob 1. čer 2024, 19:59

od DOC_ZENITH

Nepovinná/volitelná se rovná že se to nebude masovně používat, ala stejnej problém s AVX512 u Skylake-X kdy mainstream platformy je neuměly tzn pro to nikdo nevyvíjel SW, a těch pár softů co se na to nakonec vyvinulo běhá dnes lépe na AMD procesrorech.

Intel se snažil protlačit tunu věcí už mnohokrát a to i v situacích kdy byl mnohem dominantnější na trhu než je dnes. Vzpomeňme si na Intanium, optimalizace pro Netburst, atd, atd. To vše vzalo za své. Prostě něco co Intel chtěl a i přes dominantní postavení to neprotlačil. Takovejhlech věcí bylo mnoho, poslední byly ony VNNI instruce co měl Alder nést pro záchranu machine learningu poté co bylo odstřiženo AVX512 a s nim přístup k istrukcím s menší precizností které CPU uměl. A tradá používá to někdo... ne. Naopak co se těhlech věcí týče tak ZEN4 totálně dominuje nad Alderem/Raptorem. Teď se jej i MS snaží postavit na druhou kolej a vypadá to že použitelný Armový WIN se konečně stanou relitou. Intel bude rád pokud následující dekádu přežije jako akitvní výrobce a nestane se z něj další IBM. Proto tak moc investujou do fabs, protože ty dnes vydělávaj, a budou pokud se budou alespoň trochu držet v patách TSMC a budou mít co vyrábět. Co se týče architektur čipů tak Intel hraje druhé nebo třetí housle u CPU, GPU i compute akcelerátorů.

AVX10 by dávalo smysl pouze tehdy pokud by všechny instruce podporovaly všechny CPU/typy jader a ty co by je neuměly nativně by je prostě dělaly pomaleji na více průchodů, ala jak to AMD dělá s AVX512 pokud dojde na opravdu 512-bit vektory. Pokud budou určité feature nepovinné, nedočkaj se implementace do SW protože ten se nepíše tak aby fungoval je na něčem, kompatibilita je důležtější jak zbožná přání Intelu v oblacích. Btw technicky by na dobře napsaném OS neměl bejt problém pokud maj různá CPU jádra různé instrukce, scheduler by ony procesy prostě poslal tam kam patřej. Ale MS pořádně nepřepsal NT6 jádro už od Visty a Intel na ně neměl dost velkou páku, proto to dopadlo jak to dopadlo.

Re: INTEL News

Napsal: pon 3. čer 2024, 08:20

od del42sa

zrovna čerstvý příklad AMD a její ZEN5 (a to je big jádro ) ukazuje, že ani přidání více ALU a rozšíření frontendu nemusí přinést nějak závratné navýšení výkonu a Skymont nebude vyjímkou. Velká jádra Intelu jsou už teď "ultra wide" a podle toho taky vypadá ta spotřeba, Skymont není tak "tučné" jádro, ale Intel má evidentně potřebu jej také rozšiřovat, což zvyšuje počet tranzistorů a tím i spotřebu čipu, kterého primárním účelem v big/little arch. je spotřebu snižovat. Uvidíme, jaké IPC nakonec čip přinese, ale "double digit" může být klidně 10% a zbytek Intel nažene frekvencema ( opět na úkor spotřeby )

Re: INTEL News

Napsal: pon 3. čer 2024, 18:26

od Tralalák

Typický príklad pomýlenia si korelácie s kauzalitou tj. dva javy sa iba vyskytujú spolu, a to, či jeden z nich vedie k druhému, nevieme.

Vzhľadom na vyššie uvedené jeden jav opisovaný s Zen 5 nevyvoláva druhý (kauzalita) nikterak nevyvoláva predikciu o výkone Skymontu.

Proste hrušky a jablká bez akejkoľvek príčinnej súvislosti a to bez urážky.

Už nejaký ten mesiac Vás tu SNEAK PEEK-ujem.

• Silvermont / Airmont

• Goldmont

• Goldmont Plus

• Tremont

• Gracemont 2M/4M / Crestmont 2M

• Skymont 4M

so Stay tuned...

Minulotýžňový leak už dal aj nezasväteným aký taký preview... pričom zatiaľ najviac sa približuje Chips and Cheese nakoľko predsa len skúsenosti z testovania nielen mnohých malých jadier im dávajú neporovnateľnú konkurenčnú výhodu odhadnúť nielen ich výkon na rozdiel od mainstreamu veľkých jadier, ktorý pre stromy nevidí les...

zdroj: https://chipsandcheese.com/2024/05/30/t ... nt-slides/