Stránka 17 z 28

Re: AMD Steamroller/Excavator (28nm)-informace, spekulace

Napsal: stř 22. kvě 2013, 18:47

od flanker

ono to není taktem, na to mnozí zapomínají...

http://extrahardware.cnews.cz/testy/pil ... takt-4-ghz

a těch tetsů bylo mnohem více, na Planet3D, na FRhardware atd

Re: AMD Steamroller/Excavator (28nm)-informace, spekulace

Napsal: stř 22. kvě 2013, 18:58

od Hladis

Narust vykonu ve vetsine aplikaci na takt u Vishery je jak se ocekaval. U her ten narust byl vetsi nez se ocekavalo a tam to bylo vcelku prekvapeni, takze Vishera je vykonejsi takt na takt nez Zambezi + pak se pricita vyssi frekvence.

Re: AMD Steamroller/Excavator (28nm)-informace, spekulace

Napsal: stř 22. kvě 2013, 21:26

od flanker

ano, ale odkaz je srovnání takt na takt...A takt na takt je to kolem 7% pro apliakce a kolem 15% pro hry. S vlastními stock takty je to pak okolo 10% v aplikacích a i kolem 17-25% v hrách....

Re: AMD Steamroller/Excavator (28nm)-informace, spekulace

Napsal: stř 22. kvě 2013, 22:20

od Hladis

Ja napsal to samy, jen bez uvedeni %

Re: AMD Steamroller/Excavator (28nm)-informace, spekulace

Napsal: sob 25. kvě 2013, 22:40

od flanker

údajně Steamroller die jádra (že by Kaveri?)

Re: AMD Steamroller/Excavator (28nm)-informace, spekulace

Napsal: sob 25. kvě 2013, 23:55

od yuri.cs

Pekne! Je to nejaky Family 15h a BD ani PD to nejsou. Na prvni pohled pomerne velke zmeny v L1 I-cache. Od boku bych typnul, ze by to i mohl byt SR.

//Je to minimalne SR.

http://abload.de/img/srbtus1.png

//jenom ta FPU je totalne divna - takhle symetricka byt nemuze. Bud to muze byt retusovane, nebo ma tahle vec dvojnasobou FPU (pro kazde jadro?).

Re: AMD Steamroller/Excavator (28nm)-informace, spekulace

Napsal: ned 26. kvě 2013, 09:06

od flanker

mohl by to někdo v nějakém editoru označit? Jednotlivé bloky v jádře?

Re: AMD Steamroller/Excavator (28nm)-informace, spekulace

Napsal: ned 26. kvě 2013, 10:28

od THANATOS

No ak je to Kaveri, tak to vyzerá na významné zmeny a potenciálne slušný nárast výkonu, hlavne v FP podľa toho obrázku.

Re: AMD Steamroller/Excavator (28nm)-informace, spekulace

Napsal: ned 26. kvě 2013, 10:36

od flanker

zjednodušeně se dá říci, že vlastně Steamroller je Bulldozer 2.generace.

Re: AMD Steamroller/Excavator (28nm)-informace, spekulace

Napsal: ned 26. kvě 2013, 11:06

od yuri.cs

flanker píše:mohl by to někdo v nějakém editoru označit? Jednotlivé bloky v jádře?

Na hrubo:

http://abload.de/img/sr2hguql.png

Problem je ten, ze AMD neoznamilo tak razantni zmeny a na Excavator je brzy. L1I je rozdelena na 2 ROMkou pro mikrokod. Je porad sdielna? Cela ta obri FPU vypada zvlastne. FPU ma nejenze zdvojene PRF ale i 2x scheduler + retire logiku. Je porad sdilena? 4 ALUs+AGUs/jadro?!

Jestli je to fake, tak si nekdo dal docela maknul...

//lepsi obrazek

Re: AMD Steamroller/Excavator (28nm)-informace, spekulace

Napsal: ned 26. kvě 2013, 14:20

od del42sa

Zajímavé, pokud by ale byl zdvojeny i fetch a FPU je to ještě vůbec Bulldozer architektura ? To by popiralo původní myšlenku modulů se sdílenými částmi a nejblíže by takové CPU mělo k původnímu uspořádání jader ala K10.

Re: AMD Steamroller/Excavator (28nm)-informace, spekulace

Napsal: ned 26. kvě 2013, 15:54

od ttxman

del42sa píše:Zajímavé, pokud by ale byl zdvojeny i fetch a FPU je to ještě vůbec Bulldozer architektura ? To by popiralo původní myšlenku modulů se sdílenými částmi a nejblíže by takové CPU mělo k původnímu uspořádání jader ala K10.

Ja myslim, ze myslenka bulldozeru byla ve sdileni casti CPU (hlavne FPU) za ucelem zmensit cip.

FPU intelu puvodne zvladala vetsinu AVX instrukci za 2 takty, ted uz by to melo byt snad vsechno za 1 takt. Haswell pokud vim zdojnasobuje vektorovy jednotky, takze teoreticky by mohl mit v nekterych pripadech 2 nasobny vykon.

Takze pridani dalsi kompletni FPU dava smysl, FP vykon na "jadro" se priblizi intelu a ve vektorovejch instrukcich to srovna pripadnej naskok haswellu.

Me by spis zajimalo, jestli obe FPU (nebo jedna zdvojena nebo co to bude) bude moc vyuzivat jenom 1 vlakno, to by mohlo slusne nakopnout single-thread vykon. Nebo by mohli rovnou zavyst spekulativni multi threading v ramci modulu, to by teprve bylo zajimavy...

Re: AMD Steamroller/Excavator (28nm)-informace, spekulace

Napsal: ned 26. kvě 2013, 20:48

od del42sa

ttxman píše:

Ja myslim, ze myslenka bulldozeru byla ve sdileni casti CPU (hlavne FPU) za ucelem zmensit cip.

FPU intelu puvodne zvladala vetsinu AVX instrukci za 2 takty, ted uz by to melo byt snad vsechno za 1 takt. Haswell pokud vim zdojnasobuje vektorovy jednotky, takze teoreticky by mohl mit v nekterych pripadech 2 nasobny vykon.

Takze pridani dalsi kompletni FPU dava smysl, FP vykon na "jadro" se priblizi intelu a ve vektorovejch instrukcich to srovna pripadnej naskok haswellu.

Me by spis zajimalo, jestli obe FPU (nebo jedna zdvojena nebo co to bude) bude moc vyuzivat jenom 1 vlakno, to by mohlo slusne nakopnout single-thread vykon. Nebo by mohli rovnou zavyst spekulativni multi threading v ramci modulu, to by teprve bylo zajimavy...

U BD šlo hlavně o snížení spotřeby a větší vytížení FPU jako takové. viz:

http://pctforum.tyden.cz/viewtopic.php? ... 0#p8433610

Jinak kromě 256 bit AVX instrukcí, které BD zpracovává jako dvě 128bit instrukce, už je flex FPU v podstatě zdvojená, protože každé jádro má k dispozici vlastní 128bit FMAC pipeline a žádné jádro nemusí zahálet při zpracovávání FPU instrukcí. Ono hypotetícké zdvojení FPU by spíše zmanenalo, že by obě jádra mohly zpracovávat AVX instrukce najednou, jinak je to ale overkill mít tolik FPU pipelines, protože bys je ani nedokázal nakrmit..... AVX2 má být ale až u Excavátoru, tak zatím nevím co si o té rozšířené FPU myslet.

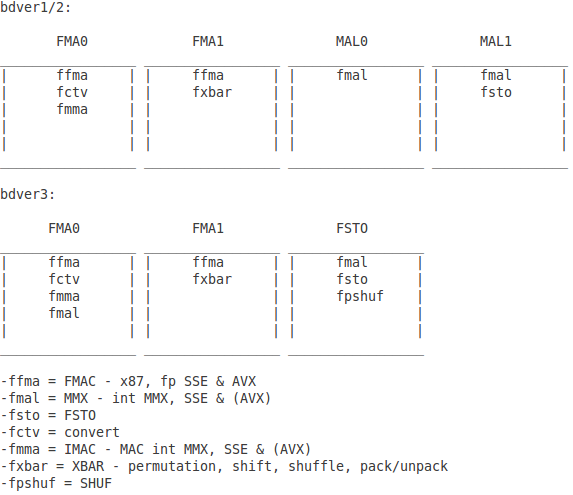

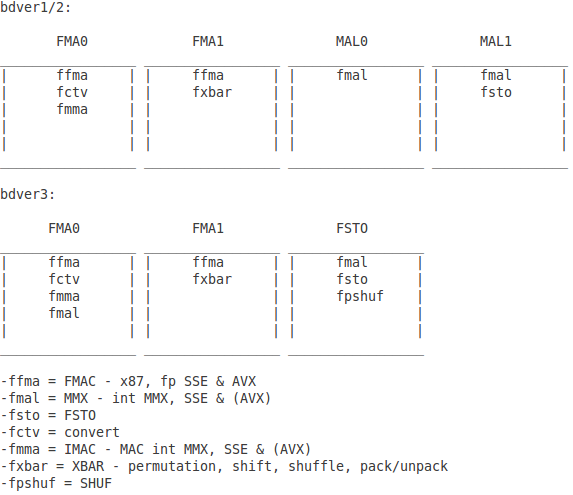

současný BD zpracovává FPU instrukce takto:

FPU Bulldozer/Vishera:

FPU Steamroller

FPU Steamroller:

Re: AMD Steamroller/Excavator (28nm)-informace, spekulace

Napsal: ned 26. kvě 2013, 21:13

od yuri.cs

Nu, ale porad jsou tam nezdvojene porty - treba FXBAR, FSTO, atd. Tam musi zafungovat vylucni drzeni zdroje 1 ze 2 threadu.

Asi nejucelenejsi analyza dieshotu je tady:

http://forum.beyond3d.com/showpost.php? ... ostcount=6

Dokud ale fellix nerekne, odkud to je (IEEE review?), tak je to celkem zbytecne...

Re: AMD Steamroller/Excavator (28nm)-informace, spekulace

Napsal: ned 26. kvě 2013, 21:20

od THANATOS

Dobrá správa je, že na Intel cpu to nevyzerá

,ale ak je to FAKE

Re: AMD Steamroller/Excavator (28nm)-informace, spekulace

Napsal: ned 26. kvě 2013, 23:40

od del42sa

No však se to už brzy dozvíme, Kaveri tu bude o vánocích 2013 (pokud vše půjde dobře) nicméně pokud to není jen dobře udělaný fake, tak by ty změny svědčily spíše pro excavator než pro steamroller vzhledem k tomu co bylo oznámeno loni na Hot Chips......

Re: AMD Steamroller/Excavator (28nm)-informace, spekulace

Napsal: stř 29. kvě 2013, 23:43

od yuri.cs

Steamroller/Kaveri letos na Hot Chips prezentovan nebude. Namisto toho budou omilat Richland a jeho teplotne zavisle Turbo...

http://www.hotchips.org/

Re: AMD Steamroller/Excavator (28nm)-informace, spekulace

Napsal: čtv 30. kvě 2013, 09:34

od flanker

krucinál

Re: AMD Steamroller/Excavator (28nm)-informace, spekulace

Napsal: pon 26. srp 2013, 23:01

od del42sa

nějaké drby o SR:

AMD took several measures to improve CPU performance and enhance functionality. For one, AMD increases the L1 instruction cache size from 64KB to 96KB and changes it's associativity from 2-way to 3-way. For virtualization, Steamroller now supports a virtualized interrupt controller, which is an advanced feature of AMD's hardware virtualization. Additionally the XSAVEOPT instruction is now supported.

...

The document lists the following changes to improve instructions per clock (IPC):

Store to load forwarding optimization

Dispatch and retire up to 2 stores per cycle

Improved memfile, from last 3 stores to last 8 stores, and allow tracking of dependent stack operations.

Load queue (LDQ) size increased to 48, from 44.

Store queue (STQ) size increased to 32, from 24.

Increase dispatch bandwidth to 8 INT ops per cycle (4 to each core), from 4 INT ops per cycle (4 to just 1 core). 4 ops per cycle per core remains unchanged.

Accelerate SYSCALL/SYSRET.

Increased L2 BTB size from 5K to 10K and from 8 to 16 banks.

Improved loop prediction.

Increase PFB from 8 to 16 entries; the 8 additional entries can be used either for prefetch or as a loop buffer.

Increase snoop tag throughput.

Change from 4 to 3 FP pipe stages.

Re: AMD Steamroller/Excavator (28nm)-informace, spekulace

Napsal: pon 26. srp 2013, 23:22

od yuri.cs

del42sa píše:nějaké drby o SR

clanek BSN z brezna...