Stránka 48 z 77

Re: Intel Cypress Cove, Golden Cove (Rocket lake/Alder lake)

Napsal: pon 18. říj 2021, 08:40

od yuri.cs

petsild píše: ↑ned 17. říj 2021, 18:36

Bude možné E cores v biosu deaktivovat a používat W10 bez omezení?

Intel to umoznuje. Zalezi na tom, jak moc hloupi budou vyrobci desek - budto tu polozku ve svem BIOSu ponechaji a nebo ji tam nedaji.

Re: Intel Cypress Cove, Golden Cove (Rocket lake/Alder lake)

Napsal: pon 18. říj 2021, 09:31

od del42sa

petsild píše: ↑ned 17. říj 2021, 18:36

Bude možné E cores v biosu deaktivovat a používat W10 bez omezení?

taky bude možné vypnout P-cores a nechat jen E-cores.

Re: Intel Cypress Cove, Golden Cove (Rocket lake/Alder lake)

Napsal: pon 18. říj 2021, 10:29

od DOC_ZENITH

V nejhoršim by to mělo jít zaříznout i normal ve win omezenim počtu CPU. Vypadá to totiž že E-cores josu v pořadu jader až za HT. Tzn když to člověk omezí na 16 měl by se zbavit oněch E-cores. Omezovat to ale timhle způsobem může podělat funkci C-states a turba.

Dobrý je že zaříznou to ve win tímto způsobem je dost efektivní a CPU co jsou "vzadu" to opravdu vůbec neinicializuje. I u mého quad CPU setupu tak třeba když to omezim na počet jader odpovídající jen CPU1, tak win naběhnou jako single CPU systém bez NUMA i když pci-e a RAM jsou některý připojený k jinejm CPU.

Re: Intel Cypress Cove, Golden Cove (Rocket lake/Alder lake)

Napsal: úte 19. říj 2021, 07:27

od del42sa

https://www.cnews.cz/na-alder-lake-nemu ... ko-denuvo/

btw u toho Alder Lake mě zaujala poznámka z Anandtechu:

With +8% for single thread in mind, the +80% in MT comparing 4 cores of Gracemont to two fully loaded Skylake cores seems a little low – we’ve got double the physical cores with Gracemont compared to Skylake here. But there’s likely some additional performance regression with the cache structure on the new Atom core, which we’ll get to later on this page.Overall, Intel stated that the E-cores are tuned for voltage more than anything else (such as performance, area). This means that the E-cores are set to use a lot less power, which may help in mobile scenarios. But as mentioned before on the first page, it will depend on how much power the ring has to consume in that environment - it should be worth noting that each four core Atom cluster only has a single stop on the full ring in Alder Lake, which Intel says should not cause congestion but it is a possibility – if each core is fully loaded, there is only 512 KB of L2 cache per core before making the jump to main memory, which indicates that in a fully loaded scenario, that might be a bottleneck.

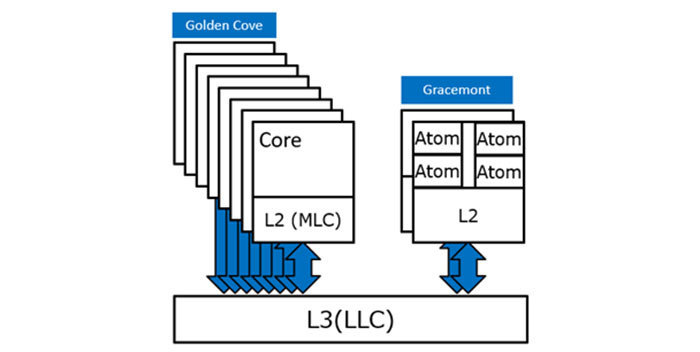

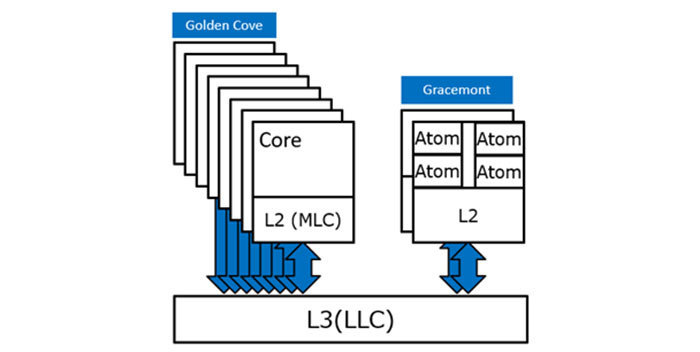

Ukazuje se také, že všechna jádra budou mít přístup do sdílené paměti L3 cache, ovšem Golden Cove jej budou mít výlučný pro každé jádro, zatímco Gracemont se budou chovat jako klastry čtyř jader, jež budou mít sdílenou L2 cache a do L3 budou přistupovat jejím prostřednictvím.

Re: Intel Cypress Cove, Golden Cove (Rocket lake/Alder lake)

Napsal: úte 19. říj 2021, 09:04

od Krteq

Jop, to je i vidět ze schématu co nedávno uvolnil Intel

Re: Intel Cypress Cove, Golden Cove (Rocket lake/Alder lake)

Napsal: úte 19. říj 2021, 10:15

od DOC_ZENITH

del42sa píše: ↑úte 19. říj 2021, 07:27

https://www.cnews.cz/na-alder-lake-nemu ... ko-denuvo/

btw u toho Alder Lake mě zaujala poznámka z Anandtechu:

With +8% for single thread in mind, the +80% in MT comparing 4 cores of Gracemont to two fully loaded Skylake cores seems a little low – we’ve got double the physical cores with Gracemont compared to Skylake here. But there’s likely some additional performance regression with the cache structure on the new Atom core, which we’ll get to later on this page.Overall, Intel stated that the E-cores are tuned for voltage more than anything else (such as performance, area). This means that the E-cores are set to use a lot less power, which may help in mobile scenarios. But as mentioned before on the first page, it will depend on how much power the ring has to consume in that environment - it should be worth noting that each four core Atom cluster only has a single stop on the full ring in Alder Lake, which Intel says should not cause congestion but it is a possibility – if each core is fully loaded, there is only 512 KB of L2 cache per core before making the jump to main memory, which indicates that in a fully loaded scenario, that might be a bottleneck.

Ukazuje se také, že všechna jádra budou mít přístup do sdílené paměti L3 cache, ovšem Golden Cove jej budou mít výlučný pro každé jádro, zatímco Gracemont se budou chovat jako klastry čtyř jader, jež budou mít sdílenou L2 cache a do L3 budou přistupovat jejím prostřednictvím.

Del tenhle citát je o ničem. Jsou tu 2 faktory který moc nezmiňuje.

1. Cache per core je o ničem. Důležité je kolik a jaké cache je k dispozici pro 1 proces, protože přes ní taky probíhá výměna dat mezi jádry. Tzn jde o SW a kolik ten rád cache, ne kolik jader na ní je. Dam příklad, pokud mam hru co se rozleze na dejme tomu 6-8threadů a CPU má 20MB L3 tak je fuk jestli při tom má 8 nebo 50 jader a moc se toho nezmění ani kdybych na těch free jádrech spustil cinebench. Znam pár úloh co potřebujou určitou velikost cache na thread (různé minery, či AI upscalery) a ty to dotahly tak daleko že na SK-X ani nemůžou pustit tolik threadů kolik jich CPU má protože prostě dojde cache a výkon by naopak padal dolu. To už ale vypichuju atypické scénáře, pointa je že počítat cache na počet jader je zcestné.

2. U ringbusu platilo že offline jádra nezatěžujou cache. Tzn stav kdy mam na ringu třeba 20 zastávek ( 4 mem controllery, 2xQPI gate a 14 jader třeba), a pak jdu a 4 CPU jádra vypnu tak cache bude mít o ony 4 stopy méně a lepší latenci. Ala tyhle stopy tam nejsou na trvo a daj se řídit. Pokud bude thread director pracovat jak má a Atom jádra zrovna nebudou loaded, můžou to vyladit tak že nemusej cache brzdit prakticky vůbec. Kor když se dušovali že cache půjde dynamicky přepínat na inclusive a non-iclusive dle typu zátěže, na což jsem dost zvědavej.

//Baneshee - promaz OT

Re: Intel Cypress Cove, Golden Cove (Rocket lake/Alder lake)

Napsal: úte 19. říj 2021, 10:18

od Tralalák

Kde asi spravili teda inžinieri chybu keď už cluster štyroch Tremont na platforme Jasper Lake zdielal L3 cache.

A asi netreba pripomínať, že Gracemont je evolúciou Tremontu...

Re: Intel Cypress Cove, Golden Cove (Rocket lake/Alder lake)

Napsal: úte 19. říj 2021, 10:20

od del42sa

DOC_ZENITH píše: ↑úte 19. říj 2021, 10:15

Del tenhle citát je o ničem. Jsou tu 2 faktory který moc nezmiňuje.

1. Cache per core je o ničem. Důležité je kolik a jaké cache je k dispozici pro 1 proces, protože přes ní taky probíhá výměna dat mezi jádry. Tzn jde o SW a kolik ten rád cache, ne kolik jader na ní je. Dam příklad, pokud mam hru co se rozleze na dejme tomu 6-8threadů a CPU má 20MB L3 tak je fuk jestli při tom má 8 nebo 50 jader a moc se toho nezmění ani kdybych na těch free jádrech spustil cinebench. Znam pár úloh co potřebujou určitou velikost cache na thread (různé minery, či AI upscalery) a ty to dotahly tak daleko že na SK-X ani nemůžou pustit tolik threadů kolik jich CPU má protože prostě dojde cache a výkon by naopak padal dolu. To už ale vypichuju atypické scénáře, pointa je že počítat cache na počet jader je zcestné.

2. U ringbusu platilo že offline jádra nezatěžujou cache. Tzn stav kdy mam na ringu třeba 20 zastávek ( 4 mem controllery, 2xQPI gate a 14 jader třeba), a pak jdu a 4 CPU jádra vypnu tak cache bude mít o ony 4 stopy méně a lepší latenci. Ala tyhle stopy tam nejsou na trvo a daj se řídit. Pokud bude thread director pracovat jak má a Atom jádra zrovna nebudou loaded, můžou to vyladit tak že nemusej cache brzdit prakticky vůbec. Kor když se dušovali že cache půjde dynamicky přepínat na inclusive a non-iclusive dle typu zátěže, na což jsem dost zvědavej.

že je o ničem nesouhlasím...., tohle se ukáže až se otestují právě ty kritické scénáře. Za normálních okolností k takové situaci nemusí vůbec dojít, ale že k ní nedojde nelze vyloučit .

@Tralalák: nejde o to že má sdílenou cache , ale jak do ní ta CPU přistupují. A ty jako "důkaz" postneš klasický Atom , který není big.little.... co na to říct ?

Re: Intel Cypress Cove, Golden Cove (Rocket lake/Alder lake)

Napsal: úte 19. říj 2021, 10:39

od Krteq

@Doc: Právě bude záležet na tom, jak bude ten RB roundtrip řešenej ... uvidíme za pár dní

Re: Intel Cypress Cove, Golden Cove (Rocket lake/Alder lake)

Napsal: úte 19. říj 2021, 12:26

od mr.qeg

Jinak, pro pomalejší - Gracemont má sdílenou L3 úplně stejně, jako GoldenCove, problém je v tom, že její obsah si 1 jádro GC přečte naráz, kdežto Gracemont bude muset jít po 512Kb chuncích (když je tam asi jen 1 port) pro každý 4-jádrový klastr, což může být bottleneck, ale zřejmě to bylo uděláno v rámci power-savingu. Skylake samozřejmě toto omezení taky neměl.

EDIT: Baneshee - opět promaz OT. Komentujte laskavě jen když máte co říct k tématu. Spekulace o tom, koho má nebo nemá Intel zaměstnávat si nechejte od cesty.

Re: Intel Cypress Cove, Golden Cove (Rocket lake/Alder lake)

Napsal: úte 19. říj 2021, 16:22

od petsild

del42sa píše: ↑úte 19. říj 2021, 07:27

https://www.cnews.cz/na-alder-lake-nemu ... ko-denuvo/

btw u toho Alder Lake mě zaujala poznámka z Anandtechu:

With +8% for single thread in mind, the +80% in MT comparing 4 cores of Gracemont to two fully loaded Skylake cores seems a little low – we’ve got double the physical cores with Gracemont compared to Skylake here. But there’s likely some additional performance regression with the cache structure on the new Atom core, which we’ll get to later on this page.Overall, Intel stated that the E-cores are tuned for voltage more than anything else (such as performance, area). This means that the E-cores are set to use a lot less power, which may help in mobile scenarios. But as mentioned before on the first page, it will depend on how much power the ring has to consume in that environment - it should be worth noting that each four core Atom cluster only has a single stop on the full ring in Alder Lake, which Intel says should not cause congestion but it is a possibility – if each core is fully loaded, there is only 512 KB of L2 cache per core before making the jump to main memory, which indicates that in a fully loaded scenario, that might be a bottleneck.

Ukazuje se také, že všechna jádra budou mít přístup do sdílené paměti L3 cache, ovšem Golden Cove jej budou mít výlučný pro každé jádro, zatímco Gracemont se budou chovat jako klastry čtyř jader, jež budou mít sdílenou L2 cache a do L3 budou přistupovat jejím prostřednictvím.

Další hřeb do rakve pro Intel, jak přemluvím Ubisoft, aby vydal update třeba na Assassin's Creed Origins?

Re: Intel Cypress Cove, Golden Cove (Rocket lake/Alder lake)

Napsal: stř 20. říj 2021, 11:06

od Sobo

Nekdo pretaktoval P-cores u 12900K na 5.2 Ghz allcore (E-cores nechal default 3.7 Ghz) - udajne to pak zralo 330W:

https://videocardz.com/newz/intel-core- ... w-of-power

To asi neni az tak prekvapujici - posledni generace AMD i Inteli jsou uz z vyroby vyhnane prakticky do maxima skrze agresivni turba, kdy manualnim OC uz clovek zadny realny benefit neziska. Taky jeden z duvodu, proc skoncilo Sillicon lottery.

Re: Intel Cypress Cove, Golden Cove (Rocket lake/Alder lake)

Napsal: stř 20. říj 2021, 11:17

od python.p

... ámen.

Poslední co mělo význam taktovat byly možná Coffe Lake.

Re: Intel Cypress Cove, Golden Cove (Rocket lake/Alder lake)

Napsal: stř 20. říj 2021, 13:56

od del42sa

Já myslím, že si Alder Lake svoje zákazníky najde, navzdory nedostatkům. Pro hardcore hráče bude neodolatný ten single thread, achilovou patou bude big-little což lze obejít volbou vhodného SKU. Spotřebu prý hráči neřeší, takže to zřejmě není problém. Škoda, že s nákupem musí člověk počítat s komplet novou platformou a pro early adopters i s DDR5.

https://wccftech.com/intel-core-i9-1290 ... -11-lower/

MSI expects DDR5 memory to be 50 to 60% more expensive than DDR4

Re: Intel Cypress Cove, Golden Cove (Rocket lake/Alder lake)

Napsal: čtv 21. říj 2021, 10:17

od Tralalák

Intel Core i9-12900K má maximálnu frekvenciu Turbo Boost Max 3.0 5,0 GHz

• veľké corové P-jadrá Golden Cove 3.6GHz až 5.0GHz

• MALÉ atómové E-jadrá Gracemont 2.7GHz až 3.8GHz

zdroj: https://videocardz.com/newz/intel-core- ... -confirmed

Re: Intel Cypress Cove, Golden Cove (Rocket lake/Alder lake)

Napsal: čtv 21. říj 2021, 10:38

od DOC_ZENITH

Až 5Ghz? Nemělo to bejt 5,2-5,3? Už se nám to ňák začíná seřezávat dolu ojojoj.

Re: Intel Cypress Cove, Golden Cove (Rocket lake/Alder lake)

Napsal: čtv 21. říj 2021, 10:57

od Sobo

To je bez TVB, takze kdo vi, kolik to nakonec bude. Mozna zjistili, ze proti AMD to bude stacit, tak to nezenou az tak na krev?

Anebo rezignovali, protoze vi, ze jsou stejne v hajzlu?

Uvidime, co nam Intel povi pristi stredu, ale vzhledem k tomu, ze ve svoji prezentaci vydavali i 11900K jako lepsi herni procesor nez Ryzen 5900X, tak bych od nich moc necekal.

Re: Intel Cypress Cove, Golden Cove (Rocket lake/Alder lake)

Napsal: čtv 21. říj 2021, 10:59

od skaven321

mne to pride, ze doteraz vonku hodili vysledky platinum cipov(tych troch co maju), a do predaja pojdu bezne silver/bronze

Re: Intel Cypress Cove, Golden Cove (Rocket lake/Alder lake)

Napsal: čtv 21. říj 2021, 11:21

od Tralalák

Re: Intel Cypress Cove, Golden Cove (Rocket lake/Alder lake)

Napsal: čtv 21. říj 2021, 11:33

od skaven321

takze nic sa nemeni a amd nebude musiet zlacnovat

, 12600 bude stat cca 300- 330€, ryzen 5 5600x stoji 280-290€, 12700K cca 500€, r7 5800X stoji 380-400€