Procesory AMD 15h "Bulldozer&Bobcat"- info, testy, spekulace

Moderátoři: flanker, Eddward, Baneshee

- richie08

- Začátečník

- Registrován: 15. říj 2006

Re: Procesory AMD K11 "Bulldozer&Bobcat"- info, testy, spekulace

Pokud zmiňuji podobnost K11 s K6, tak jen a pouze z hlediska počtu instrukcí za takt (IPC). K6 měla 2 IPC, další generace (K7, K8, K10) pak 3 IPC. Pokud má mít K11 Bulldozer pouze 2 IPC, pak by to byl krok zpět ve výkonu aritmeticko-logických operacích. To mi ale vůbec nepasuje dohromady s novou, mnohem výkonější 128-bit FPU. Čím déle nad tím přemýšlím, tak tím víc mi připadá 2IPC u Bulldozeru jako nesmysl. Bobcat a Bulldozer nejspíš budou dvě úplně ale úplně rozdílná jádra - asi tak "podobná" jako Atom s Nehalemem. Tedy Bobcat nebude očesaný Bulldozer, ale spíš od základu nový CPU. Ty Federmannovy schémata mi v tomhle světle začínají připadat jako fake.

Naopak takový Bobcat s 2 IPC mi připadá velmi reálný. Koneckonců Atom má také 2 IPC, ale bez out-ot-order a spekulativního vykonávání. Bobcat může být i přes pouhé 2 IPC o dost rychlejší než Atom, řekl bych někde na 80-90% výkonu Turionu K8 - což pro mobilní segment a netbooky bude naprosto dostatečné.

Naopak takový Bobcat s 2 IPC mi připadá velmi reálný. Koneckonců Atom má také 2 IPC, ale bez out-ot-order a spekulativního vykonávání. Bobcat může být i přes pouhé 2 IPC o dost rychlejší než Atom, řekl bych někde na 80-90% výkonu Turionu K8 - což pro mobilní segment a netbooky bude naprosto dostatečné.

- mr.qeg

- Začátečník

-

- Registrován: 05. srp 2007

- Bydliště: Dresden

Re: Procesory AMD K11 "Bulldozer&Bobcat"- info, testy, spekulace

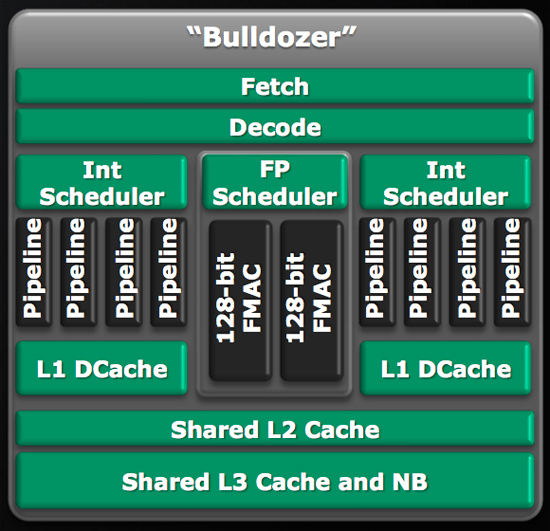

Mě by jen zajímalo, když ve všech prezentacích bylo znázorňováno JEDNO JÁDRO Bulldozeru, proč všichni automaticky spekulují, že to budou 2 jádra? Já jsem to teda pochopil tak, že je znázorněno jedno jádro (ALU, FPU, ALU) a při tom AMD "Hypertreadingu" bude možno sdílet tu FPU ( ne že se budou programy bít o jednotky jak u Intelu)a každá jedna ALU pro jiný thread. Nebo mi něco uniká?

- Federmann

- Začátečník

- Registrován: 16. kvě 2006

- Kontaktovat uživatele:

Re: Procesory AMD K11 "Bulldozer&Bobcat"- info, testy, spekulace

richie08 píše: Ty Federmannovy schémata mi v tomhle světle začínají připadat jako fake.

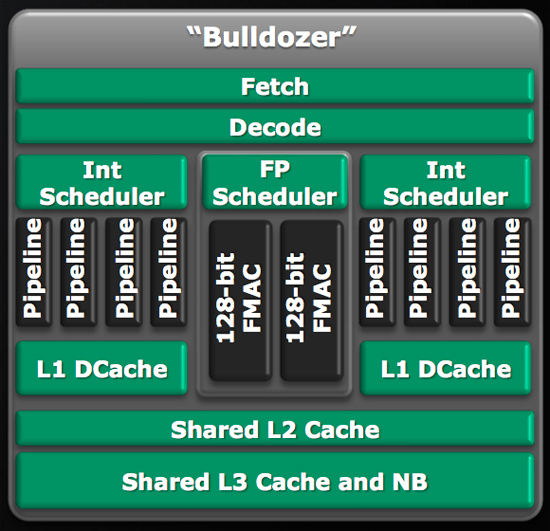

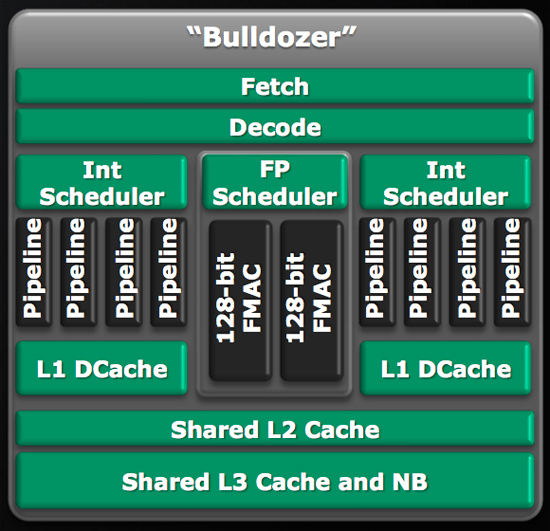

flanker píše:Takže malá newska k Bulldozer jádru. Jeden modul níže

V čem je takový rozdíl?Federmann píše:Dal bych obrázky, ale nevejdou se tak jen odkazy.

http://www.federmann.cz/images/stories/ ... ozer_1.jpg

http://www.federmann.cz/images/stories/ ... ozer_2.jpg

http://www.federmann.cz/images/stories/ ... ozer_3.jpg

AMD patent květen 1996

Mám i velikost jádra cca 160mm2

- richie08

- Začátečník

- Registrován: 15. říj 2006

Re: Procesory AMD K11 "Bulldozer&Bobcat"- info, testy, spekulace

2 mr.qeg: Jj, jak píše F. - takhle by to mělo být správně: 1x Bulldozer modul = 2x Bulldozer jádra.

2 Federmann: tak rozdíl je především v tom, že ty AMD slidy znázorňují 4x "pipeline" (za nimiž se mohou skrývat 4x ALU), kdežto ty druhé schémata 2x ALU + 2 load/store jednotky. Zvláště v porovnání s K10 (3xALU + 3xLSU) vypadá nová architektura trošku podivně poddimenzovaně. Vysvětlíš mi proč by měl být Bulldozer výkonější i s pouhými dvěmi ALUs než K10? Ať si trochu zaspekulujeme...

2 Federmann: tak rozdíl je především v tom, že ty AMD slidy znázorňují 4x "pipeline" (za nimiž se mohou skrývat 4x ALU), kdežto ty druhé schémata 2x ALU + 2 load/store jednotky. Zvláště v porovnání s K10 (3xALU + 3xLSU) vypadá nová architektura trošku podivně poddimenzovaně. Vysvětlíš mi proč by měl být Bulldozer výkonější i s pouhými dvěmi ALUs než K10? Ať si trochu zaspekulujeme...

- Federmann

- Začátečník

- Registrován: 16. kvě 2006

- Kontaktovat uživatele:

Re: Procesory AMD K11 "Bulldozer&Bobcat"- info, testy, spekulace

Já na tom nic divného nevidím K10 = 3xALU+3xAGU, Bulldozer K11= 4xALU+4xAGU, v podstatě 2xK6, další změny v Micro-OPS …

- yuri.cs

- Mírně pokročilý

- Registrován: 03. led 2007

- Bydliště: hl.m. piva

- Kontaktovat uživatele:

Re: Procesory AMD K11 "Bulldozer&Bobcat"- info, testy, spekulace

2 IPC na jadro by byly zatracene malo a ohromny krok zpet. Na tech F. diagramech jsou u K11 vsude symboly '?' a "estimated", cili jen a jen spekulace

It will be amazing in case after 10GHz we will see 20GHz, 30GHz and so on, just like we witnessed the thorny way from 10MHz to 33MHz in the eighties. -xbitlabs.com

- Federmann

- Začátečník

- Registrován: 16. kvě 2006

- Kontaktovat uživatele:

Re: Procesory AMD K11 "Bulldozer&Bobcat"- info, testy, spekulace

Jak jsem napsal na svých stránkách, poněkud se začíná vytrácet definice jádra. Zřejmě nemusí jít vždy jako Multithreading, pak to platí, jak píši, pokud Multithreading poběží, pak se jádro pomyslně rozdělí a nepere se o vlákno, má blíže ke dvěma fyzickým jádrům, navíc se vytrácí název jádro a je nahrazeno názvem modul.

- flanker

- Moderátor

- Registrován: 13. pro 2005

- Bydliště: Brno

- Kontaktovat uživatele:

Re: Procesory AMD K11 "Bulldozer&Bobcat"- info, testy, spekulace

v první generaci by nás měly čekat 4-moduly ("osmijádra") Zdali to bude stačit na 8-jádrový "Gulftown", to těžko říci...

ROG Power PC1:AMD Ryzen 7 5700X, Crosshair VII Hero, ROG Ryuo II 360, 512GB NVMe+500GB Samsung SSD, 2x 16GB GSkill TridentZ Neo RGB 3600 MHz, Dual RTX 2060,CM V750, Lian Li O11 Dynamic XL. PC2:AMD FX-8370, Silentium Fera, Asus 970 Pro Gaming/Aura, 240GB SSD HyperX 3K, R9-270X OC, 2x 4GB GSkill RipjawsX 2400 MHz, Corsair AX750, Bitfenix Pandora

- yuri.cs

- Mírně pokročilý

- Registrován: 03. led 2007

- Bydliště: hl.m. piva

- Kontaktovat uživatele:

Re: Procesory AMD K11 "Bulldozer&Bobcat"- info, testy, spekulace

Gulftown 8 jader je virtualni 16 jadro... Cili AMD bude konkurovat cenou.

Jinak dle citavia blogu to stale vic vypada, ze K11 je optimalizovana pro vysoke f... cili takovy 32nm NetBurst :/

Jinak dle citavia blogu to stale vic vypada, ze K11 je optimalizovana pro vysoke f... cili takovy 32nm NetBurst :/

It will be amazing in case after 10GHz we will see 20GHz, 30GHz and so on, just like we witnessed the thorny way from 10MHz to 33MHz in the eighties. -xbitlabs.com

- flanker

- Moderátor

- Registrován: 13. pro 2005

- Bydliště: Brno

- Kontaktovat uživatele:

Re: Procesory AMD K11 "Bulldozer&Bobcat"- info, testy, spekulace

Dresdenboy o Bulldozeru: This was just an argument against the per core performance analysis. What counts is how fast your apps run with what energy consumption and at which price. Also matters become more complex because of more advanced energy management methods etc. Recently I tried to scale back the Interlagos performance advantage to 4 and 6 cores (2 and 3 modules respectively) and got performance numbers comparable to 4.8 and 3.8 GHz quad- and six-core K10. OTOH I also already heard, that BD scales really well. This would mean somewhat lower numbers for the smaller core counts.

And then add an even more efficient turbo for the lowly threaded apps or even such ones, which don't utilize some of the units that much (e.g. FPU, caches).. We might see scalable caches, TLBs, FPUs, maybe even integer cores... A lot of such stuff has been patented. So I don't have problems to agree with informal here.

And then add an even more efficient turbo for the lowly threaded apps or even such ones, which don't utilize some of the units that much (e.g. FPU, caches).. We might see scalable caches, TLBs, FPUs, maybe even integer cores... A lot of such stuff has been patented. So I don't have problems to agree with informal here.

ROG Power PC1:AMD Ryzen 7 5700X, Crosshair VII Hero, ROG Ryuo II 360, 512GB NVMe+500GB Samsung SSD, 2x 16GB GSkill TridentZ Neo RGB 3600 MHz, Dual RTX 2060,CM V750, Lian Li O11 Dynamic XL. PC2:AMD FX-8370, Silentium Fera, Asus 970 Pro Gaming/Aura, 240GB SSD HyperX 3K, R9-270X OC, 2x 4GB GSkill RipjawsX 2400 MHz, Corsair AX750, Bitfenix Pandora

- THANATOS

- Začátečník

-

- Registrován: 14. zář 2009

- Bydliště: Nové Zámky

Re: Procesory AMD K11 "Bulldozer&Bobcat"- info, testy, spekulace

Uz len nastava otazka, ze na akej frekvencii bol ten Interlagos a ci bol 4modulovy. Ale ked zoberieme, ze by bol na 2.6GHz a 4modulovy tak oproti 4jadrovemu by bol narast nieco okolo 85% co vyzera dost slusne. Ked si zoberieme ze je to tiez stvorjadro s niekolkymi castami zdvojenymi hlavne ALU a niektorymi nie, FPU jednotka jedna na modul a asi chache tiez nebude zdvojena.

Lenovo Legion Y540-15IRH CPU: Intel Core i5 9300H GPU: NVIDIA GeForce GTX 1650 4GB RAM: 24GB 2666Mhz Micron SSD: 512GB WDC SN720 + 1TB Crucial MX500

- flanker

- Moderátor

- Registrován: 13. pro 2005

- Bydliště: Brno

- Kontaktovat uživatele:

Re: Procesory AMD K11 "Bulldozer&Bobcat"- info, testy, spekulace

Objevila se spekulace, vycházející ze společné prezentace MS o windows 7 a AMD, že Bulldozer nakonec bude tvořen pro jiný socket než AM3+...Je to pouze spekulace, ale trochu mě to zarazilo. Napadá mě jedi ná možná myšlenka. Bulldozer architektura bude dělaná v podobném duchu jako dnes Nehalem/Lynfiled apod...tzn. byl by nějaký mainstreamový 4 core model pro s AM3+/AM3 a highend 6-8 jádrový do zcela nového socketu.

ROG Power PC1:AMD Ryzen 7 5700X, Crosshair VII Hero, ROG Ryuo II 360, 512GB NVMe+500GB Samsung SSD, 2x 16GB GSkill TridentZ Neo RGB 3600 MHz, Dual RTX 2060,CM V750, Lian Li O11 Dynamic XL. PC2:AMD FX-8370, Silentium Fera, Asus 970 Pro Gaming/Aura, 240GB SSD HyperX 3K, R9-270X OC, 2x 4GB GSkill RipjawsX 2400 MHz, Corsair AX750, Bitfenix Pandora

- richie08

- Začátečník

- Registrován: 15. říj 2006

Re: Procesory AMD K11 "Bulldozer&Bobcat"- info, testy, spekulace

Někteří tady straší s Netburstem kvůli údajným vysokým frekvencím K11. Myslím, že se stačí podívat na vývoj pipeline stage u Intelu: P3 (10-stage), P4 (20-stage Willamete, 31-stage Prescott). Čím delší pipeline, tím vyšší frekvence mohu dosáhnout. Pokud by byla pipeline ideálně navržena, pak by frekvence rostla lineárně.

Mnohem zajímavější je ale vývoj architektury P6 (tedy bez exota P4): P3 (10-stage, 1.3GHz max), P-M (12/14-stage Banias/Dothan, 2.2GHz max), Core1 (12-stage, taky kolem 2.2GHz), Core2 (14-stage, zhruba 3GHz), Nehalem (16-stage, 3.6GHz). Ty frekvence jsou odhad co si pamatuji, ale i tak je zde jasně vidět, že pipeline se prodlužuje pro dosažení vyšších frekvencí. Evoluce je to nevyhnutelná, protože rychlost tranzistorů se zmenšujícím se výrobním procesem již neroste lineárně. Paradoxně tak Sandybridge bude mít pipeline dlouhou skoro/stejně jako P4 Willamete. A není na tom nic špatného.

Vývoj u AMD je podobný, leč mnohem konzervativnější: K7 (10-stage), K8 (12-stage), K10 (12-stage). U FPU to byl skok z 15 (K7) -> 17 (K8/10) stage. Zde je vidět, že K10 je velmi zdařilou evolucí K8 a je docela obdivuhodné vidět na jakých frekvencích ty čipy běhají i s tak krátkou pipeline. Na konečnou frekvenci má ale velký vliv i výrobní proces, konkrétně drahý SOI proces má výrazněji zrychlovat tranzistory, takže těžko soudit zcela objektivně. Z pohledu délky pipeline bude K11 jistě mnohem vyspělejší - očekával bych pipeline delší než 14, někde mezi 16-18? Zatím můžeme jen spekulovat. Jisté je, že moderní CPU budou mít pipeline čím dál delší a rozhodně to neznamená, že dopadnou stejně neslavně jako P4. Ať tedy bude Bulldozer K11 jakýkoliv, zcela jistě bude díky delší pipeline běhat na vyšších frekvencích než Deneb.

Mnohem zajímavější je ale vývoj architektury P6 (tedy bez exota P4): P3 (10-stage, 1.3GHz max), P-M (12/14-stage Banias/Dothan, 2.2GHz max), Core1 (12-stage, taky kolem 2.2GHz), Core2 (14-stage, zhruba 3GHz), Nehalem (16-stage, 3.6GHz). Ty frekvence jsou odhad co si pamatuji, ale i tak je zde jasně vidět, že pipeline se prodlužuje pro dosažení vyšších frekvencí. Evoluce je to nevyhnutelná, protože rychlost tranzistorů se zmenšujícím se výrobním procesem již neroste lineárně. Paradoxně tak Sandybridge bude mít pipeline dlouhou skoro/stejně jako P4 Willamete. A není na tom nic špatného.

Vývoj u AMD je podobný, leč mnohem konzervativnější: K7 (10-stage), K8 (12-stage), K10 (12-stage). U FPU to byl skok z 15 (K7) -> 17 (K8/10) stage. Zde je vidět, že K10 je velmi zdařilou evolucí K8 a je docela obdivuhodné vidět na jakých frekvencích ty čipy běhají i s tak krátkou pipeline. Na konečnou frekvenci má ale velký vliv i výrobní proces, konkrétně drahý SOI proces má výrazněji zrychlovat tranzistory, takže těžko soudit zcela objektivně. Z pohledu délky pipeline bude K11 jistě mnohem vyspělejší - očekával bych pipeline delší než 14, někde mezi 16-18? Zatím můžeme jen spekulovat. Jisté je, že moderní CPU budou mít pipeline čím dál delší a rozhodně to neznamená, že dopadnou stejně neslavně jako P4. Ať tedy bude Bulldozer K11 jakýkoliv, zcela jistě bude díky delší pipeline běhat na vyšších frekvencích než Deneb.

- yuri.cs

- Mírně pokročilý

- Registrován: 03. led 2007

- Bydliště: hl.m. piva

- Kontaktovat uživatele:

Re: Procesory AMD K11 "Bulldozer&Bobcat"- info, testy, spekulace

Neexistuje nahodou jista korelace mezi delkou pipeliny a slozitosti predikcnich obvodu? Vetsina lidi ma v pameti Prescotty@3.6GHz se 150W, proto ten "strach" s vysoke frekvence :/

It will be amazing in case after 10GHz we will see 20GHz, 30GHz and so on, just like we witnessed the thorny way from 10MHz to 33MHz in the eighties. -xbitlabs.com

- richie08

- Začátečník

- Registrován: 15. říj 2006

Re: Procesory AMD K11 "Bulldozer&Bobcat"- info, testy, spekulace

Ano, čím delší pipeline tím větší ztráty při špatné predikci kódu. S vývojem lepších predikčních algoritmů a lepších kompilátorů si mohou výrobci CPU dovolit i delší pipeline. Řeč je ale o evoluci, Intel jde postupně z 10-stage přes 12, 14, až na nynějších 16. Proto bych nesrovnával s P4 kde to skočilo z 10-stage (P3) na 20 a pak na 31. Další věc proč nesrovnávat s P4 je v její úplně jiné koncepci: vysoká frekvence (marketing) a nizké IPC (což měly kompenzovat ALUs běžící na 7.6GHz). Zatímco dnešní moderní CPU jdou jednoduše za max výkonem: max IPC a zároveň max frekvence.yuri.cs píše:Neexistuje nahodou jista korelace mezi delkou pipeliny a slozitosti predikcnich obvodu? Vetsina lidi ma v pameti Prescotty@3.6GHz se 150W, proto ten "strach" s vysoke frekvence :/

Pokud K11 Bulldozer bude mít lepší výkon na takt oproti Intelu třeba o 20%, pak to bude k ničemu pokud poběží na frekvenci 2GHz. A je jedno jestli to bude vinou architektury nebo výrobního procesu jako Barcelona.

- flanker

- Moderátor

- Registrován: 13. pro 2005

- Bydliště: Brno

- Kontaktovat uživatele:

Re: Procesory AMD K11 "Bulldozer&Bobcat"- info, testy, spekulace

o taktech tšžko řící, již o prvním Fusion se mluví, že to budou procesory frekvence vyšší než 3GHz. Snady Bridge sahá v top modelech až někdě k 3.8 GHz (s turbem/bez turba???)

PS:pánové, omlouvám se za svoje nedostatky ohledně detailů architektur jak a co funguje, mohl by sjte mi někdo odkázat na článek (nejlépe v cz), kde bych lépe porozuměl vaší diskuzi? Díky.

PS:pánové, omlouvám se za svoje nedostatky ohledně detailů architektur jak a co funguje, mohl by sjte mi někdo odkázat na článek (nejlépe v cz), kde bych lépe porozuměl vaší diskuzi? Díky.

ROG Power PC1:AMD Ryzen 7 5700X, Crosshair VII Hero, ROG Ryuo II 360, 512GB NVMe+500GB Samsung SSD, 2x 16GB GSkill TridentZ Neo RGB 3600 MHz, Dual RTX 2060,CM V750, Lian Li O11 Dynamic XL. PC2:AMD FX-8370, Silentium Fera, Asus 970 Pro Gaming/Aura, 240GB SSD HyperX 3K, R9-270X OC, 2x 4GB GSkill RipjawsX 2400 MHz, Corsair AX750, Bitfenix Pandora

- yuri.cs

- Mírně pokročilý

- Registrován: 03. led 2007

- Bydliště: hl.m. piva

- Kontaktovat uživatele:

Re: Procesory AMD K11 "Bulldozer&Bobcat"- info, testy, spekulace

Se zamerem kompenzace nizke hodnoty IPC vysokou frekvenci, ktera se jeste tenkrat dala skvele vyuzit v marketingu, souhlasim

Spojeni "max IPC+max f" zni velice jednoduse. Hodnotu IPC ovlivnuje rada faktoru, matne tusim ze existuje i spojitost s poctem stages pipeliny.

Spojeni "max IPC+max f" zni velice jednoduse. Hodnotu IPC ovlivnuje rada faktoru, matne tusim ze existuje i spojitost s poctem stages pipeliny.

It will be amazing in case after 10GHz we will see 20GHz, 30GHz and so on, just like we witnessed the thorny way from 10MHz to 33MHz in the eighties. -xbitlabs.com

- ttxman

- Začátečník

-

- Registrován: 28. zář 2003

Re: Procesory AMD K11 "Bulldozer&Bobcat"- info, testy, spekulace

Flanker: tady máš takový výtah. Pokud bys měl zájem o materiály z vysoké školy (docela se to dá i číst napiš mi PMku)

Instrukce v CPU se zpracovává v několika fázích, a to i v procesoru bez zřetězeného zpracování.

4 základní stupně zpracování instrukce vypadají nějak takhle.

1) načtení instrukce 2) dekódování instrukce 3)provedení instrukce 4)uložení výsledku.

Pokud procesor nezpracovává instrukce zřetězeně (pipeline) potřebuje na vykonání 1 instrukce několik taktů (v tomto případě 4) .

Pokud by měl tento procesor 4 stupňovou pipeline znamenalo by to, že každý stupeň zpracování instrukce je možné vykonávat nezávisle a tedy v každém stupni může být jedna instrukce bez toho aby se čekalo na dokončení předchozí.

U typu RISC instrukční sady trvá každá instrukce stejně taktů a tedy pipeline se bude plynule posunovat s každým taktem CPU. U CISC (x86 původně) mají instrukce různou dobu zpracování a tedy některá fáze zpracování mohou trvat různé počty taktů a posun nebude tak plynulý jako v příkladě níž. (jak je to s dnešními CPU upřesním dole... CPU zůstane v 3. fázi 2 cykly a tak se načtení další instrukce o jeden takt zdrží, tomu se říká bublina nebo anglicky bubble, kdyby někdo čet třeba anglickou Wikipedii)

Princip spočívá v tom, že jakmile instrukce opustí jednu fázi zpracování, je tato fáze obsazena další instrukcí v pořadí.

V prvním taktu se načte 1. instrukce. (ostatní 3 stupně pipeline jsou nevytížené)

V druhém taktu se načte 2. instrukce a zároveň dekóduje 1. (2 stupně pipeline jsou nevytížené)

V dalším taktu se načte 3. instrukce, dekóduje 2. a provede první. (1 stupeň je nevytížený)

Ve čtvrtém taktu se načte 4. instrukce, dekóduje 3., provede 2. a zapíše se výsledek 1. (pipeline plně vytížena)

V pátém taktu by to už bylo:

Načte se 5. instrukce, dekóduje 4., provede 3. a zapíše se výsledek 2. (pipeline plně vytížena)

Takže od 4. taktu by už CPU produkovalo výsledek v každém taktu místo každého čtvrtého taktu. A dosáhli jsme tak 4 násobného zrychlení procesoru jen přidáním 4 stupňové pipeline.

Problém by byl, kdyby jedna z instrukcí byla podmíněný skok. Typicky pak procesor nenačítá další instrukce dokud není jasné (z výsledku předchozí instrukce) kam program odskočil a tedy jaká je vlastně další instrukce v pořadí. (a tím se zase pipeline vyprazdňuje a klesá efektivita)

V moderních CPU existuje jakási predikce kam by to skočit mohlo a instrukce se tedy načítají dál. V případě že se predikce spletla jsou výsledky zahozeny a dojde k načtení instrukcí z místa kam to odskočit mělo(U 4 stupňové pipeline se výsledek získá ve 4 taktu zpracování instrukce a tak se musí zahodit 3 následující. A procesor pak další výsledek zapíše zase za další 4 takty, u 31 stupňů je to 30 zahozených instrukcí a další výsledek za 31 taktů). V případě, že se predikce povede procesor pokračuje dál a v každém taktu provede další instrukci.

Teď jakou to má souvislost s takty CPU:

Čím víc stupňů pipeline, tím jednoduší obvod je potřeba na každý stupeň. Čím jednodušší obvod tím na vyšší frekvenci může teoreticky pracovat. Proto taky Intel tvrdil, že Netburst bude moct fungovat na vysokých taktech, i když to tak nakonec nedopadlo.

V moderních x86(x64) CPU ještě před samotným zpracováním instrukce (CISC nejsou zpracovatelné stejně rychle) dojde k přeložení na vnitřní mikroinstrukce procesoru a ty už jsou všechny zpracovatelné za stejný počet taktů.

NetBurst měl v L1 cache uložené už právě mikroinstrukce, čímž se mělo zrychlit načtení instrukcí v případě, že došlo k chybě při předvídání skoku. (nemusel se dělat překlad, ušetřila se nějaké doba)

Edit: Pipeline není jediný způsob jak zrychlit zpracování instrukcí. V dnešních CPU se toho kombinuje víc.

Například jde zpracovávat několik instrukcí plně najednou (v každé fázi zpracování by mohly být 2 a více instrukce), to se může kombinovat s pipeline => tak se načtou v každém taktu 2 instrukce, dekódují 2 instrukce, vypočítají 2 instrukce, zapíše výsledek 2 instrukcí. (a v případě, že první v páru byla skok se druhá ,může zahodit atd.)

Instrukce v CPU se zpracovává v několika fázích, a to i v procesoru bez zřetězeného zpracování.

4 základní stupně zpracování instrukce vypadají nějak takhle.

1) načtení instrukce 2) dekódování instrukce 3)provedení instrukce 4)uložení výsledku.

Pokud procesor nezpracovává instrukce zřetězeně (pipeline) potřebuje na vykonání 1 instrukce několik taktů (v tomto případě 4) .

Pokud by měl tento procesor 4 stupňovou pipeline znamenalo by to, že každý stupeň zpracování instrukce je možné vykonávat nezávisle a tedy v každém stupni může být jedna instrukce bez toho aby se čekalo na dokončení předchozí.

U typu RISC instrukční sady trvá každá instrukce stejně taktů a tedy pipeline se bude plynule posunovat s každým taktem CPU. U CISC (x86 původně) mají instrukce různou dobu zpracování a tedy některá fáze zpracování mohou trvat různé počty taktů a posun nebude tak plynulý jako v příkladě níž. (jak je to s dnešními CPU upřesním dole... CPU zůstane v 3. fázi 2 cykly a tak se načtení další instrukce o jeden takt zdrží, tomu se říká bublina nebo anglicky bubble, kdyby někdo čet třeba anglickou Wikipedii)

Princip spočívá v tom, že jakmile instrukce opustí jednu fázi zpracování, je tato fáze obsazena další instrukcí v pořadí.

V prvním taktu se načte 1. instrukce. (ostatní 3 stupně pipeline jsou nevytížené)

V druhém taktu se načte 2. instrukce a zároveň dekóduje 1. (2 stupně pipeline jsou nevytížené)

V dalším taktu se načte 3. instrukce, dekóduje 2. a provede první. (1 stupeň je nevytížený)

Ve čtvrtém taktu se načte 4. instrukce, dekóduje 3., provede 2. a zapíše se výsledek 1. (pipeline plně vytížena)

V pátém taktu by to už bylo:

Načte se 5. instrukce, dekóduje 4., provede 3. a zapíše se výsledek 2. (pipeline plně vytížena)

Takže od 4. taktu by už CPU produkovalo výsledek v každém taktu místo každého čtvrtého taktu. A dosáhli jsme tak 4 násobného zrychlení procesoru jen přidáním 4 stupňové pipeline.

Problém by byl, kdyby jedna z instrukcí byla podmíněný skok. Typicky pak procesor nenačítá další instrukce dokud není jasné (z výsledku předchozí instrukce) kam program odskočil a tedy jaká je vlastně další instrukce v pořadí. (a tím se zase pipeline vyprazdňuje a klesá efektivita)

V moderních CPU existuje jakási predikce kam by to skočit mohlo a instrukce se tedy načítají dál. V případě že se predikce spletla jsou výsledky zahozeny a dojde k načtení instrukcí z místa kam to odskočit mělo(U 4 stupňové pipeline se výsledek získá ve 4 taktu zpracování instrukce a tak se musí zahodit 3 následující. A procesor pak další výsledek zapíše zase za další 4 takty, u 31 stupňů je to 30 zahozených instrukcí a další výsledek za 31 taktů). V případě, že se predikce povede procesor pokračuje dál a v každém taktu provede další instrukci.

Teď jakou to má souvislost s takty CPU:

Čím víc stupňů pipeline, tím jednoduší obvod je potřeba na každý stupeň. Čím jednodušší obvod tím na vyšší frekvenci může teoreticky pracovat. Proto taky Intel tvrdil, že Netburst bude moct fungovat na vysokých taktech, i když to tak nakonec nedopadlo.

V moderních x86(x64) CPU ještě před samotným zpracováním instrukce (CISC nejsou zpracovatelné stejně rychle) dojde k přeložení na vnitřní mikroinstrukce procesoru a ty už jsou všechny zpracovatelné za stejný počet taktů.

NetBurst měl v L1 cache uložené už právě mikroinstrukce, čímž se mělo zrychlit načtení instrukcí v případě, že došlo k chybě při předvídání skoku. (nemusel se dělat překlad, ušetřila se nějaké doba)

Edit: Pipeline není jediný způsob jak zrychlit zpracování instrukcí. V dnešních CPU se toho kombinuje víc.

Například jde zpracovávat několik instrukcí plně najednou (v každé fázi zpracování by mohly být 2 a více instrukce), to se může kombinovat s pipeline => tak se načtou v každém taktu 2 instrukce, dekódují 2 instrukce, vypočítají 2 instrukce, zapíše výsledek 2 instrukcí. (a v případě, že první v páru byla skok se druhá ,může zahodit atd.)

- richie08

- Začátečník

- Registrován: 15. říj 2006

Re: Procesory AMD K11 "Bulldozer&Bobcat"- info, testy, spekulace

2 flanker: svoje znalosti si průběžně průběžně doplňuji čtením zahraničních článků. A bohužel také průběžně dost zapomínám  Zkus tohle http://cs.wikipedia.org/wiki/Pipelining Zrovna nedávno jsem četl někde pod zahraničním článkem v diskuzi o problematice pipeline. Jedná se o to, že všechny stupně pipeline musí trvat ideálně stejný čas tak, aby se vešly mezi jednotlivé takty procesoru. No a protože náboj se šíří určitou rychlostí a tranzistor na překlopení stavu také potřebuje nějaký čas, je rozhodující čas za který dotyčným obvodem projde signál na výstup. A je jasné, že 5-stage CPU (jedna stage dlouhá 100 tranzistorů) bude pracovat na nižší frekvenci než 10-stage CPU (jedna stage dlouhá 50 tranzistorů).

Zkus tohle http://cs.wikipedia.org/wiki/Pipelining Zrovna nedávno jsem četl někde pod zahraničním článkem v diskuzi o problematice pipeline. Jedná se o to, že všechny stupně pipeline musí trvat ideálně stejný čas tak, aby se vešly mezi jednotlivé takty procesoru. No a protože náboj se šíří určitou rychlostí a tranzistor na překlopení stavu také potřebuje nějaký čas, je rozhodující čas za který dotyčným obvodem projde signál na výstup. A je jasné, že 5-stage CPU (jedna stage dlouhá 100 tranzistorů) bude pracovat na nižší frekvenci než 10-stage CPU (jedna stage dlouhá 50 tranzistorů).

2 yuri.cs: IPC ... nevím jak by mohla přímo ovlivňovat délku pipeline. IPC ovlivňuje paralelismus (superskalárnost) zatímco délka pipeline serialismus (rychlost vykonávání instrukcí). Asi by nebyl problém udělat CPU s 8 IPC a 30-stage pipeline. Problém by asi byl, že by zabral tolik tranzistorů jako dnešní 4-jádro přičemž výkon by byl mnohem nižší.

2 yuri.cs: IPC ... nevím jak by mohla přímo ovlivňovat délku pipeline. IPC ovlivňuje paralelismus (superskalárnost) zatímco délka pipeline serialismus (rychlost vykonávání instrukcí). Asi by nebyl problém udělat CPU s 8 IPC a 30-stage pipeline. Problém by asi byl, že by zabral tolik tranzistorů jako dnešní 4-jádro přičemž výkon by byl mnohem nižší.

- ttxman

- Začátečník

-

- Registrován: 28. zář 2003

Re: Procesory AMD K11 "Bulldozer&Bobcat"- info, testy, spekulace

K tomu IPC:

Scalar pipeline - (nebo taky jenom pipeline) nejjednodusi pipeline urcena k dosazeni 1 instrukce za tak v idealnich podminkach (max IPC = 1)

EN wiki

Superscalar Pipeline - uplny paralelizmus mozno dosahnout IPC>1.

EN wiki .. prvni obrazek ukazuje pipeline s IPC=2

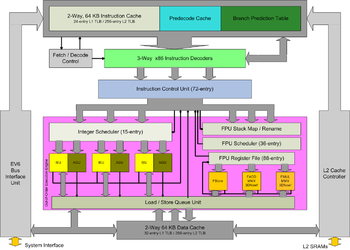

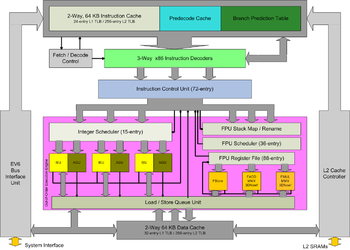

Podle toho Flankerova obrazku to vypada jakoby 1 Bulldozer modul obsahoval 2 jadra, ktera muzou sdilet matematicky casti.

Pokud bych si zaspekuloval tak ty nakresy pipeline by se dali brat jako paralelne zpracovavany vypocty. Takze tu mame neco co ma 2 cesty pro celociselny vypocty s 4 IPC a jednu cestu pro vypocty v plovouci carce s 2 IPC.

Fyzicky to vypada na CPU s dvojnasobnou 4 cestnou ALU dvojnasobnou slozitou FPU jednotkou. (FMAC). Tady se pise, ze se pipeline pro FPU obcas oddeluje a Tady je pro zmenu popis novinek co AMD v ramci FPU zavedlo do puvodnich ATHLONu, tedy ze oddelilo vypocetni cesty pro INT a FPU jednotky.

Rozeberu to trosku detailneji.

Kdyz srovnate obrazky architektur (vsechno z wikipedie)

K6 - 2*INT ALU , 1 FPU a 1 MMI (multimedialni instrukce) vsechno v jedny ceste(takze nemuze FPU a INT ALU bezet pocitat najendou ruzne ulohy)

K7 3*INT ALU a 1FPU s MMI. (FPU se samostatnou cestou)

K8 3*INT ALU (jedna slozitejsi, IMUL by mohlo byt integer multiplication). 1*FPU s MMI.

K10 3*INT ALU (dve slozitejsi, co je ten novej blocek netusim). 1*FPU s MMI.

K11

Tak K11 se proti K7-K10 jevi takhle

Pridani dalsi stage do INT casti (4 IPC?).

Rozsireni FPU jednotky na 128bit instrukce (asi hlavne pro MMI)

Zdvojnasobeni vsech vypocetnich vnitrnosti. (2*(INT ALU + FPU))

Takze se mi to jevi jako dnesni nativni dvoujadro, jenze se sdilenym nacitanim a dekodovanim instrukci.

To sdileni tam k necemu musi byt, napadaji me 3 veci, kterych by se to mohlo tykat.

1) Efektivnejsi Hyperthreading. (dalsi vlakno si muze pujcit jednotku i z druheho jadra)

2) Jednojadro, ktere ovsem fyzicky zpracovava 2 vlakna najednou, (SMTmeli uz SPARC procesory). Treba by se tim proti nativnimu dvoujadru usetril nejaky prostor. (Hmm HT je implementace SMT od intelu takze je to vlastne porad bod 1 )

)

3) Kdysi pred nastupem K10 se mluvilo o nejake technologii jako obraceny hyperthreading kde by vice jader CPU mohlo zpracovavat 1 vlakno programu. Tady mame nacitani jednoho proudu instrukci a 2* vypocetni cast CPU, takze by se urcite dalo nejake rizeni jader implementovat jednoduseji nez u klasicke koncepce 2 jadra. Takze by se 1 modul mohl prepnout do modu s 8IPC misto 4. I kdyby vykon misto 100% vzrostl o 50% porad by to bylo velmi vyhodne pro 1 vlaknovy plikace a algoritmy.

Scalar pipeline - (nebo taky jenom pipeline) nejjednodusi pipeline urcena k dosazeni 1 instrukce za tak v idealnich podminkach (max IPC = 1)

EN wiki

Superscalar Pipeline - uplny paralelizmus mozno dosahnout IPC>1.

EN wiki .. prvni obrazek ukazuje pipeline s IPC=2

Podle toho Flankerova obrazku to vypada jakoby 1 Bulldozer modul obsahoval 2 jadra, ktera muzou sdilet matematicky casti.

Pokud bych si zaspekuloval tak ty nakresy pipeline by se dali brat jako paralelne zpracovavany vypocty. Takze tu mame neco co ma 2 cesty pro celociselny vypocty s 4 IPC a jednu cestu pro vypocty v plovouci carce s 2 IPC.

Fyzicky to vypada na CPU s dvojnasobnou 4 cestnou ALU dvojnasobnou slozitou FPU jednotkou. (FMAC). Tady se pise, ze se pipeline pro FPU obcas oddeluje a Tady je pro zmenu popis novinek co AMD v ramci FPU zavedlo do puvodnich ATHLONu, tedy ze oddelilo vypocetni cesty pro INT a FPU jednotky.

Rozeberu to trosku detailneji.

Kdyz srovnate obrazky architektur (vsechno z wikipedie)

K6 - 2*INT ALU , 1 FPU a 1 MMI (multimedialni instrukce) vsechno v jedny ceste(takze nemuze FPU a INT ALU bezet pocitat najendou ruzne ulohy)

K7 3*INT ALU a 1FPU s MMI. (FPU se samostatnou cestou)

K8 3*INT ALU (jedna slozitejsi, IMUL by mohlo byt integer multiplication). 1*FPU s MMI.

K10 3*INT ALU (dve slozitejsi, co je ten novej blocek netusim). 1*FPU s MMI.

K11

Tak K11 se proti K7-K10 jevi takhle

Pridani dalsi stage do INT casti (4 IPC?).

Rozsireni FPU jednotky na 128bit instrukce (asi hlavne pro MMI)

Zdvojnasobeni vsech vypocetnich vnitrnosti. (2*(INT ALU + FPU))

Takze se mi to jevi jako dnesni nativni dvoujadro, jenze se sdilenym nacitanim a dekodovanim instrukci.

To sdileni tam k necemu musi byt, napadaji me 3 veci, kterych by se to mohlo tykat.

1) Efektivnejsi Hyperthreading. (dalsi vlakno si muze pujcit jednotku i z druheho jadra)

2) Jednojadro, ktere ovsem fyzicky zpracovava 2 vlakna najednou, (SMTmeli uz SPARC procesory). Treba by se tim proti nativnimu dvoujadru usetril nejaky prostor. (Hmm HT je implementace SMT od intelu takze je to vlastne porad bod 1

3) Kdysi pred nastupem K10 se mluvilo o nejake technologii jako obraceny hyperthreading kde by vice jader CPU mohlo zpracovavat 1 vlakno programu. Tady mame nacitani jednoho proudu instrukci a 2* vypocetni cast CPU, takze by se urcite dalo nejake rizeni jader implementovat jednoduseji nez u klasicke koncepce 2 jadra. Takze by se 1 modul mohl prepnout do modu s 8IPC misto 4. I kdyby vykon misto 100% vzrostl o 50% porad by to bylo velmi vyhodne pro 1 vlaknovy plikace a algoritmy.