Stránka 1 z 7

AMD Bobcat2/3 architektura (core Jaguar...)-infa, testy

Napsal: stř 29. srp 2012, 09:46

od flanker

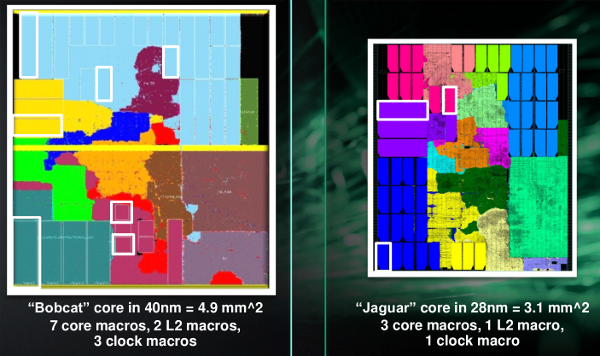

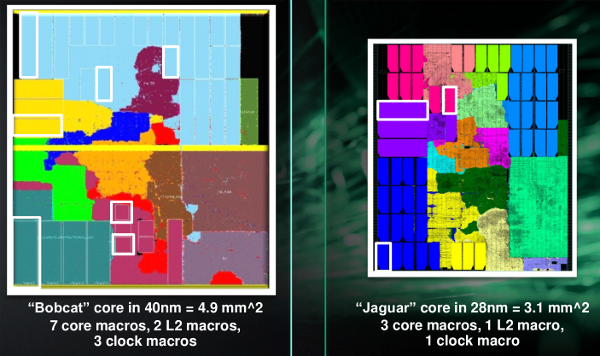

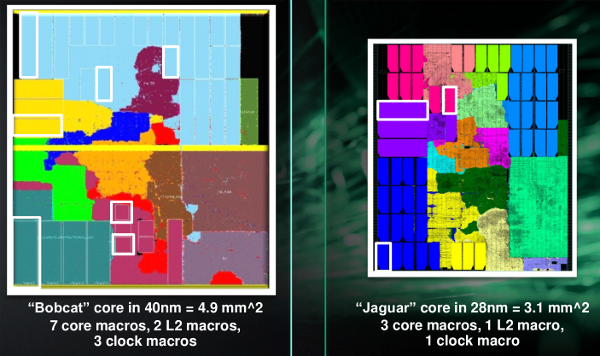

Na probíhajícím Hotchips AMD poodhalilo informace o významnějším refreshy Bobcatů.

Jádro Jaguar, nejspíš bude na 28nm, ale jisté to není. Zajímavé je i kolik toto malé jádro umí moderních instrukcí:

- SSE4.1, SSE4.2, AES, CLMUL, MOVBE, AVX, XSAVE, XSAVEOPT, FC16, BMI1

- bohužel pouze jednokanálový paměťový řadič

- L2 o velikosti 2MB

Vylepšený power gating, pokud bude procesor na 28nm, mohl by být skutečně efektivní.

Celý článek je na "Semi"

http://semiaccurate.com/2012/08/28/amd- ... guar-core/

Re: AMD Bobcat2/3 architektura (core Jaguar...)-infa, testy

Napsal: čtv 30. srp 2012, 23:16

od yuri.cs

Jaguar = AMD Family 16h

Alespon dle gcc changelogu.

* The x86 backend of GCC now supports CPUs based on AMD Family 16h cores with x86-64 instruction set support. This includes the MOVBE, F16C, BMI, AVX, PCL_MUL, AES, SSE4.2, SSE4.1, CX16, ABM, SSE4A, SSSE3, SSE3, SSE2, SSE, MMX and 64-bit instruction set extensions. This is enabled via:

-march=btver2

http://nickclifton.livejournal.com/11428.html

Re: AMD Bobcat2/3 architektura (core Jaguar...)-infa, testy

Napsal: čtv 30. srp 2012, 23:33

od del42sa

Re: AMD Bobcat2/3 architektura (core Jaguar...)-infa, testy

Napsal: pát 31. srp 2012, 20:00

od THANATOS

Re: AMD Bobcat2/3 architektura (core Jaguar...)-infa, testy

Napsal: pát 31. srp 2012, 23:37

od del42sa

28nm výrobní proces u GF by nakonec bude nejenom BULK ale i FD-SOI :

http://www.electronicsweekly.com/blogs/ ... athor.html

PS: tahle část je obzvláště zajímavá :

Chery reckons the Intel 22nm process is really a 26nm process measured by drawn gate length.

Re: AMD Bobcat2/3 architektura (core Jaguar...)-infa, testy

Napsal: ned 2. zář 2012, 00:51

od webwalker

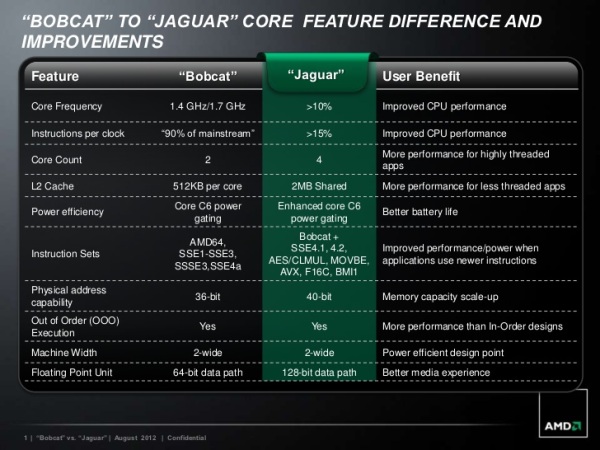

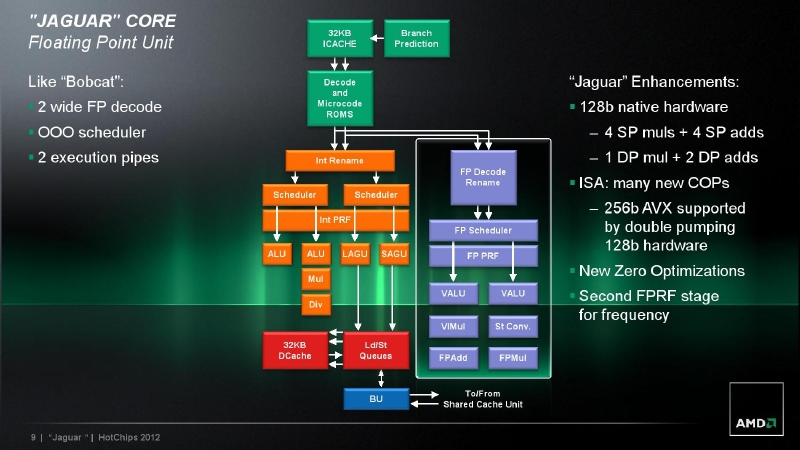

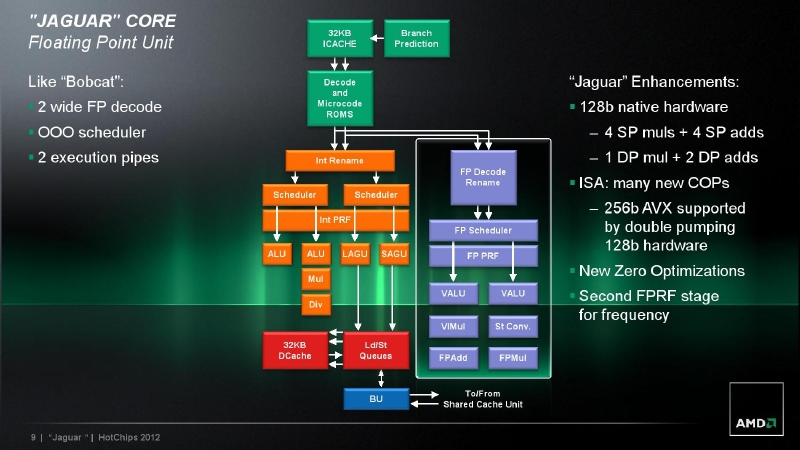

Jak si vysvětlit větu "256b AVX supported by double pumping 128b hardware"

AVX = dekódována jako jedna mops (cops) provedena ve dvou (zrychlených) taktech na jedné pipe fpu?

Re: AMD Bobcat2/3 architektura (core Jaguar...)-infa, testy

Napsal: ned 2. zář 2012, 08:56

od del42sa

webwalker píše:

Jak si vysvětlit větu "256b AVX supported by double pumping 128b hardware"

AVX = dekódována jako jedna mops (cops) provedena ve dvou (zrychlených) taktech na jedné pipe fpu?

ne ne to bude stejné jako u Bulldozeru. 256bit AVX se provede pomocí 128 bitových pipelines (bobcat měl dvě 64 bit FP pipelines) za dva cykly. (opakovaně na jedné pipeline, vycházím z předpokladu, že zatímco u BD se jedná o dvě identické FMAC pipeline, Jaguar FMAC pipeline nemá a tedy obě FP pipelines nejsou identické )

je to sice z článku o BD, ale bude to stejné i pro Jaguar.

Given the fact that for AVX the two 128-bit FMACs are ganged as opposed to the SB-architecture where AVX enables un-used resources, it is not surprising that there is not much of a difference having AVX enabled/disabled. There is still a small performance improvement, which could potentially be attributed to the fact that 256-bit instructions are FastPath Double which will generate two 128-bit macro-ops from decode. AMD claims the two 128-bit FMA units are "fused" to a single 256-bit unit, thus, it is at least conceivable that the two operations stay separate. There is still a theoretical advantage of 256-bit AVX by saving fetch and decode bandwidth, which could explain the "synthetic" performance increase.

http://www.lostcircuits.com/mambo//inde ... itstart=13

http://www.lostcircuits.com/mambo//inde ... itstart=13

proto bude AVX výkon u Jaguaru stejně patetický jako výkon u Bulldozeru. Stejně tak mnozí nechápou, proč v Steamrolleru AMD nepřidalo alespoň jednu 256 bit FMAC pipeline pro AVX (AVX2 asi SR nepodporuje ?)

Na druhou stranu je potřeba dodat (vzhledem k zatím velice pozvolnému rozšiřování AVX) že pro Jaguar bude podstatná především kompatibilita (s AVX a dalšími instrukcemi) nikoliv rychlost a že pomalé AVX tedy nebude představovat vlastně žádný handicap

U Steamrolleru je ale už situace trochu jiná, tam by měla AMD sílu FPU přehodnotit (i když dokud nebudou venku první vzorky a testy je předčasné to hodnotit, protože k nějakému FP nárustu mohlo u SR také dojít)

Re: AMD Bobcat2/3 architektura (core Jaguar...)-infa, testy

Napsal: ned 2. zář 2012, 09:41

od flanker

Ale zas musíme koukat na Jaguar jako na lowend produkt. A na ten to vypadá na slušně povedený procesor. Proč kruci AMDčku jdou dobře lowend CPUčka a ten highend je takový výkonem nevyrovnaný

...

Re: AMD Bobcat2/3 architektura (core Jaguar...)-infa, testy

Napsal: ned 2. zář 2012, 12:14

od del42sa

flanker píše:Proč kruci AMDčku jdou dobře lowend CPUčka a ten highend je takový výkonem nevyrovnaný

...

protože jde o server produkt (for server workload). Zatímco Jaguar je pro desktop/notebook segment a jádro tudíž neobsahuje žádné "serverové featury". Pokud by od Jaguaru AMD odvodilo nějaký výkonnější model schopný běhat na vyšších frekvencích (3 GHz a výše) bylo by to ideální CPU pro desktop a gaming.

Re: AMD Bobcat2/3 architektura (core Jaguar...)-infa, testy

Napsal: ned 2. zář 2012, 13:11

od webwalker

del42sa píše:

ne ne to bude stejné jako u Bulldozeru. 256bit AVX se provede pomocí 128 bitových pipelines (bobcat měl dvě 64 bit FP pipelines) za dva cykly. (opakovaně na jedné pipeline, vycházím z předpokladu, že zatímco u BD se jedná o dvě identické FMAC pipeline, Jaguar FMAC pipeline nemá a tedy obě FP pipelines nejsou identické )

To je sice pravda, jedna pipe má pouze add a druhá jen mul. Takže AVX musí být vždy řešena ve dvou taktech ve stejné pipe. "hot-clock" se tím ale nevylučuje a měl by i výhodu zpracování dvou AVX (různého typu ADD a MUL) v jednom (normálním) taktu cpu. No, ale po zkušenostech s P4 a nVidia gpu kdo by ho vlastně chtěl opět vytahovat, že

V každém případě u Jaguáru musel být zvětšen (zdvojnásoben) register file, aby bylo možné 256b (AVX) výpočty provádět ve dvou taktech.

U BD je to imho řešeno jinak. Tam musel být AVX zpracován v jednom taktu na dvou fmac současně (jinak by musel být registr také dvojnásobný).

proto bude AVX výkon u Jaguaru stejně patetický jako výkon u Bulldozeru. Stejně tak mnozí nechápou, proč v Steamrolleru AMD nepřidalo alespoň jednu 256 bit FMAC pipeline pro AVX (AVX2 asi SR nepodporuje ?)

Imho nejde předělat pouze jednu pipe na 256b. Tam se musí rozšířit kompletní "datapath" celého cpu na 256b, tedy i L/S jednotky a samozřejmě register file a bůh ví co ještě.

Na druhou stranu je potřeba dodat (vzhledem k zatím velice pozvolnému rozšiřování AVX) že pro Jaguar bude podstatná především kompatibilita (s AVX a dalšími instrukcemi) nikoliv rychlost a že pomalé AVX tedy nebude představovat vlastně žádný handicap

Pravda

U Steamrolleru je ale už situace trochu jiná, tam by měla AMD sílu FPU přehodnotit (i když dokud nebudou venku první vzorky a testy je předčasné to hodnotit, protože k nějakému FP nárustu mohlo u SR také dojít)

Myslím, že SR zůstane stále serverovým cpu i po všech těch vylepšeních. Na desktop bohužel vhodný stále nebude

Re: AMD Bobcat2/3 architektura (core Jaguar...)-infa, testy

Napsal: ned 2. zář 2012, 13:43

od del42sa

webwalker píše:

U BD je to imho řešeno jinak. Tam musel být AVX zpracován v jednom taktu na dvou fmac současně (jinak by musel být registr také dvojnásobný).

U BD se diky Flex FPU dvě 128 bit FMAC pipe chovají jako jedna 256 bitová, ale to je jen teorie. Protože ve skutečnosti se 256bit instrukce rozdělí na dvě 128 bitové (2 cykly), které se vykonají naráz. Z toho je zřejmé, že SB dokáže za stejný cyklus vykonat dvojnásobný počet AVX instrukcí per core.

Bulldozer may technically feature AVX, but its comparative performance isn’t very good, even in integer code. The i7-2600K has four FPUs — just like AMD’s chip — but it can handle 256-bit AVX instructions without splitting them into 2×128-bit chunks.

na druhou stranu u SB

If you mix 256-bit AVX instructions with legacy SSE instructions that use xmm registers, you will incur performance penalties of roughly one hundred cycles at each transition between legacy code and AVX code. This is because the processor must save the state of the upper 128-bits of the ymm registers at the first legacy instruction so that they can be restored upon issuing another AVX instruction

webwalker píše:Imho nejde předělat pouze jednu pipe na 256b. Tam se musí rozšířit kompletní "datapath" celého cpu na 256b, tedy i L/S jednotky a samozřejmě register file a bůh ví co ještě.

to máš samozřejmě pravdu, já to myslel tak, že by tam zůstaly ty dvě 128 bit FMAC + jedna 256 bit FMAC pipe navíc (nebo další dvě 128 bit FMAC). Přece jenom Intel CPU zvládají dvojnásobek FPU instrukcí oproti Bulldozeru a rozhodně se nedá říct (jak už podotknul Yuri) že by ty procesory byly nějak extrémně obrovské. Adekvátním zvětšením FPU by se o dost zvednul výkon a nemyslím, že by to ty CPU nějak extrémně zvětšilo....

Re: AMD Bobcat2/3 architektura (core Jaguar...)-infa, testy

Napsal: ned 2. zář 2012, 19:20

od THANATOS

Kludne mohli pridat dalsie FMAC, plocha by sa zvacsila minimalne, jedine by to viac papalo, ale to sa da kompenzovat o nieco nizsim taktom a voltazou. Takto stracaju vykon len preto, ze toto bolo stavane akoze pre servery.

Re: AMD Bobcat2/3 architektura (core Jaguar...)-infa, testy

Napsal: ned 2. zář 2012, 23:23

od webwalker

del42sa píše:U BD se diky Flex FPU dvě 128 bit FMAC pipe chovají jako jedna 256 bitová, ale to je jen teorie. Protože ve skutečnosti se 256bit instrukce rozdělí na dvě 128 bitové (2 cykly), které se vykonají naráz. Z toho je zřejmé, že SB dokáže za stejný cyklus vykonat dvojnásobný počet AVX instrukcí per core.

Imho, takhle to u BD nefunguje. BD AVX dekóduje do dvou mops, které stihne vykonat na dvou fmac v

jednom taktu. Při dvou taktech by fpu bylo prakticky nepoužitelné.

Přece jenom Intel CPU zvládají dvojnásobek FPU instrukcí oproti Bulldozeru...

Jak kdy a v čem

1. SSE - 128b (což jsou 2DP nebo 4SP výpočty)

1. SSE - 128b (což jsou 2DP nebo 4SP výpočty)

SB zvládne buďto 1xMUL + 1xADD (když se zadaří), nebo pouze 1xMUL nebo 1xADD (tedy 2-4DP nebo 4-8 SP)

BD zvládne jakoukoli kombinaci ADD i MUL (tedy 4DP nebo 8SP)

Teoreticky zde vyhrává BD - max. výkon sice stejný, ale BD je univerzálnější, muže i 2xADD nebo 2xMUL.

2. AVX - 256b (což jsou 4DP nebo 8SP výpočty)

SB zvládne buďto 1xMUL + 1xADD (když se zadaří), nebo pouze 1xMUL nebo 1xADD (tedy 4-8DP nebo 8-16SP)

BD zvládne buďto 1xMUL nebo 1xADD (tedy 4DP nebo 8SP)

Teoreticky zde vyhrává SB, ale pouze v případě, kdy se zadaří a v jednom taktu jsou zpracovávány instrukce jak ADD, tak i MUL na druhém portu.

3. FMA - 128b (což jsou 4DP nebo 8SP výpočty MUL+ADD)

SB nezvládne (nemá FMA)

BD zvládne 2xFMA (tedy 8DP nebo 16SP)

Teoreticky

zde vyhrává BD. Za povšimnutí stojí, že teoretický výpočetní výkon je u BD s FMA stejný nebo vyšší nežli u SB s AVX (pokud jsem se nespletl).

Do příchodu Haswellu s FMA tedy rozložení a počet ALU v FPU pro BD nevypadá zas tak tragicky - tedy vše je jen teorie.

Re: AMD Bobcat2/3 architektura (core Jaguar...)-infa, testy

Napsal: pon 3. zář 2012, 09:15

od del42sa

sice jsi to spočítal dobře, ale BD má FPU sdílenou pro dvě jádra, zatímco SB má FPU v každém jádře (byť také v rámci jádra sdílí porty). Mimo AVX instrukcí je FPU Bulldozeru opravdu dobře použitelná a srovnatelná (alespoň teoreticky) s konkurencí. Jakmile ale Bulldozer provádí AVX instrukce, tak už to taková sláva není. Kdyby měla FPU v BD čtyři 128bitové FMAC pipeline (které by pracovaly jako 2 x 256 bit AVX), tak by byl výkon někde jinde. Nakonec ty rozdíly na které jsme se už kdysi dívali jsou u BD se zapnutým AVX skoro minimální s vyjímkou linuxových testů (že by kompiler ?)

http://www.lostcircuits.com/mambo//inde ... itstart=13

http://blogs.amd.com/work/2010/10/25/the-new-flex-fp/

http://blogs.amd.com/work/2010/10/25/the-new-flex-fp/

máš SZ

Re: AMD Bobcat2/3 architektura (core Jaguar...)-infa, testy

Napsal: úte 4. zář 2012, 20:32

od yuri.cs

Re: AMD Bobcat2/3 architektura (core Jaguar...)-infa, testy

Napsal: čtv 6. zář 2012, 10:56

od webwalker

@yuri: Sujay Shrivastava

"Worked on Steamroller core (Bulldozer team) revB"

"Worked on Steamroller core (Bulldozer team) revA"

Dvě revize čipu SR?

Re: AMD Bobcat2/3 architektura (core Jaguar...)-infa, testy

Napsal: čtv 6. zář 2012, 11:10

od flanker

kdo je ten Sujay Shrivastava?

možná revize pro APU a druhá pro desktop/server?

Re: AMD Bobcat2/3 architektura (core Jaguar...)-infa, testy

Napsal: čtv 6. zář 2012, 11:12

od del42sa

od jisté doby dělají u všech nových produktů dvě verze, jedna první (testovací) použitá převážně v APU a druhá lépe odladěná (se silnějšími jádry ?) v serveru/desktopu ? už dávno se o tom spekulovalo na SA

AMD se v tom nejspíše shlídlo. Začalo to s Brazosem (verze 2.0), pak Trinity verze 1, verze 2 a Steamroller zřejmě nebude vyjímka. Kaveri APU nejspíše bude v1 a Serveroví nástupci Abudhabi a spol. verze 2. Něco jako AMD obdoba tick- tock.

http://pctforum.tyden.cz/viewtopic.php? ... 9#p8269269

\\ hmm 260%

a pak že AMD nedokáže navrhovat dobré CPU

Re: AMD Bobcat2/3 architektura (core Jaguar...)-infa, testy

Napsal: čtv 6. zář 2012, 11:26

od webwalker

Re: AMD Bobcat2/3 architektura (core Jaguar...)-infa, testy

Napsal: pon 17. zář 2012, 14:02

od del42sa

btw nevíte někdo kdy se mají objevit první notebooky /tablety s Jaguarem ?